Global security controller (GTZC) RM0453

84/1461 RM0453 Rev 1

3.4.7 Interrupts

TZIC is a secure peripheral that generates systematically an illegal access event when

accessed by a non-secure access.

TZSC is a security-aware peripheral, meaning that secure and non-secure registers

co-exist.

3.5 GTZC TZSC registers

All GTZC TZSC registers are accessed only by words (32-bit). Halfwords (16-bit) and bytes

(8-bit) accesses are denied and generate a bus error.

The TZSC MPCWM privileged control registers MPCWMn_UPWMR from the different

internal memories are defined in the table below.

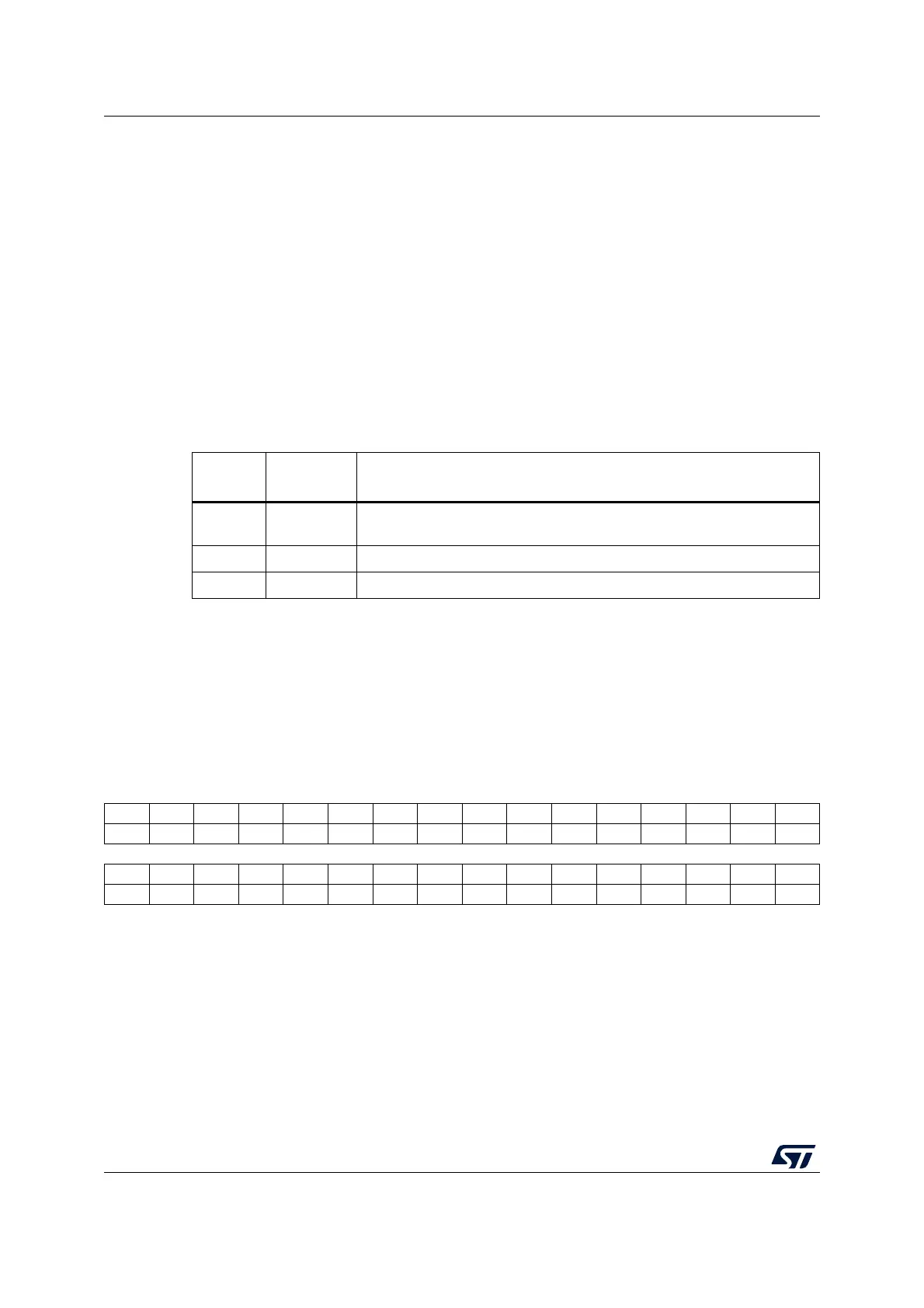

3.5.1 GTZC TZSC control register (GTZC_TZSC_CR)

Address offset: 0x000

Reset value: 0x0000 0000

Secure read and write access only

Note: When the system is non-secure (ESE = 0), this register cannot be written and is read zero.

Table 8. TZSC privileged MPCWMn register memory allocation

MPCWM

index

Memory Description

1Flash

Unprivileged and unprivileged writable control (security controlled by user

option)

2 SRAM1 Unprivileged control (security controlled by user option)

3 SRAM2 Unprivileged control (security controlled by user option)

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. LCK

rs

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 LCK: Lock the configuration of TZSC registers until next reset

The configuration is unlocked after a wakeup from Standby.

This bit is unset by default and once set, it cannot be reset until a global TZSC reset.

0: All TZSC registers not locked

1: All TZSC registers locked

Loading...

Loading...