RM0453 Rev 1 273/1461

RM0453 Power control (PWR)

276

6.6.20 PWR security configuration register (PWR_SECCFGR)

This register is not reset when exiting Standby modes.

Access: three additional APB cycles are needed to write this register versus a standard APB

write.

This register can only be accessed by a secure privileged access for read and write. Non-

secure and unprivileged accesses are ignored and return zero data. Furthermore an illegal

access event is generated.

Note: When the system is non-secure (ESE = 0), this register cannot be written and is read as 0.

Address offset: 0x08C

Reset value: 0x0000 8000

6.6.21 PWR sub-GHz SPI control register (PWR_SUBGHZSPICR)

Address offset: 0x090

Reset value: 0x0000 8000

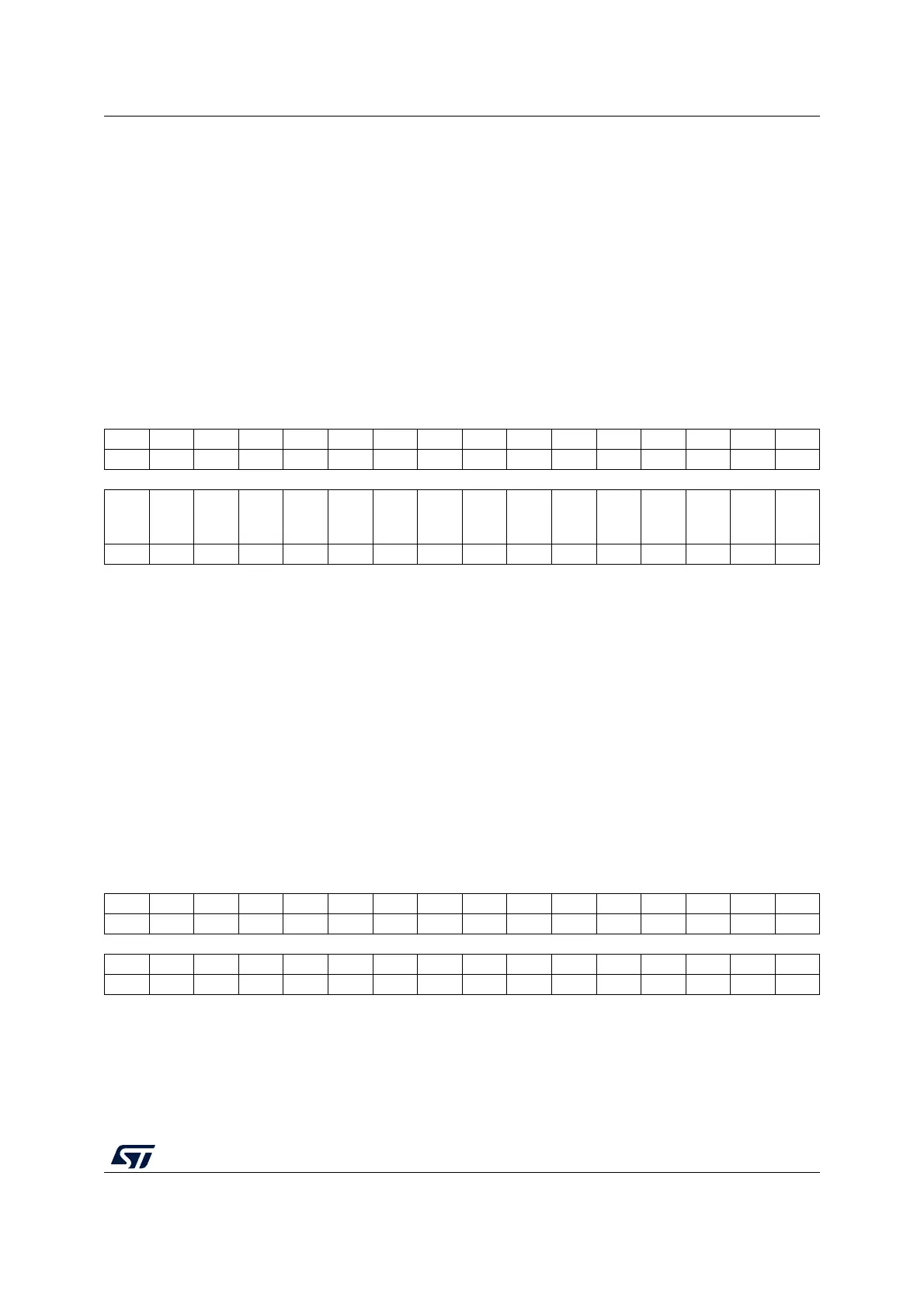

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

C2EWILA

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw

Bits 31:16 Reserved, must be kept at reset value.

Bit 15 C2EWILA: wakeup on CPU2 illegal access interrupt enable

This bit is set and cleared by software

0: CPU2 wakeup on illegal access interrupt disabled (does not wake up CPU2 from low-

power modes).

1: CPU2 wakeup on illegal access interrupt enabled (wakes up CPU2 from low-power

modes).

Bits 14:0 Reserved, must be kept at reset value.

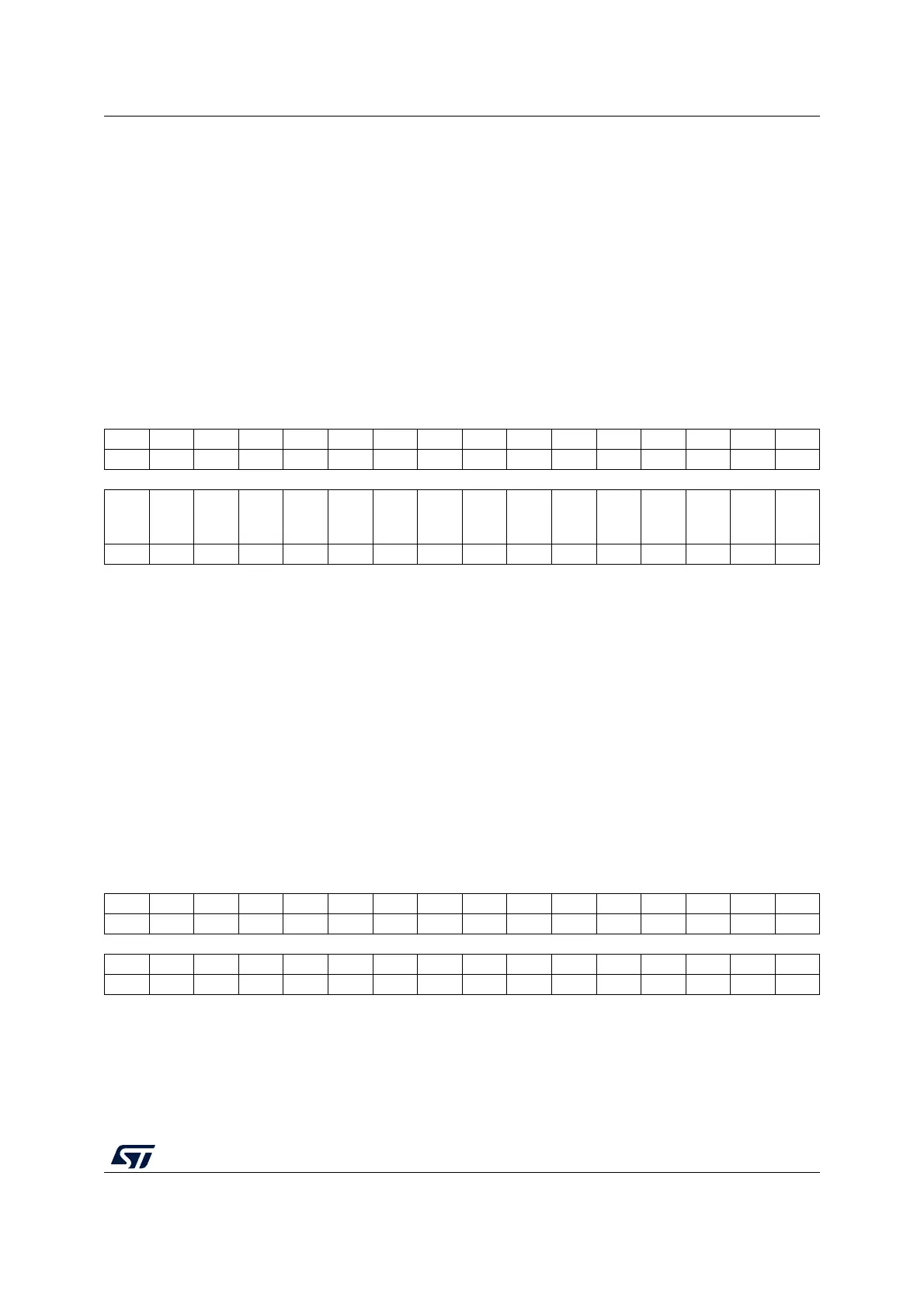

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

NSS Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

rw

Loading...

Loading...