Debug support (DBG) RM0453

1390/1461 RM0453 Rev 1

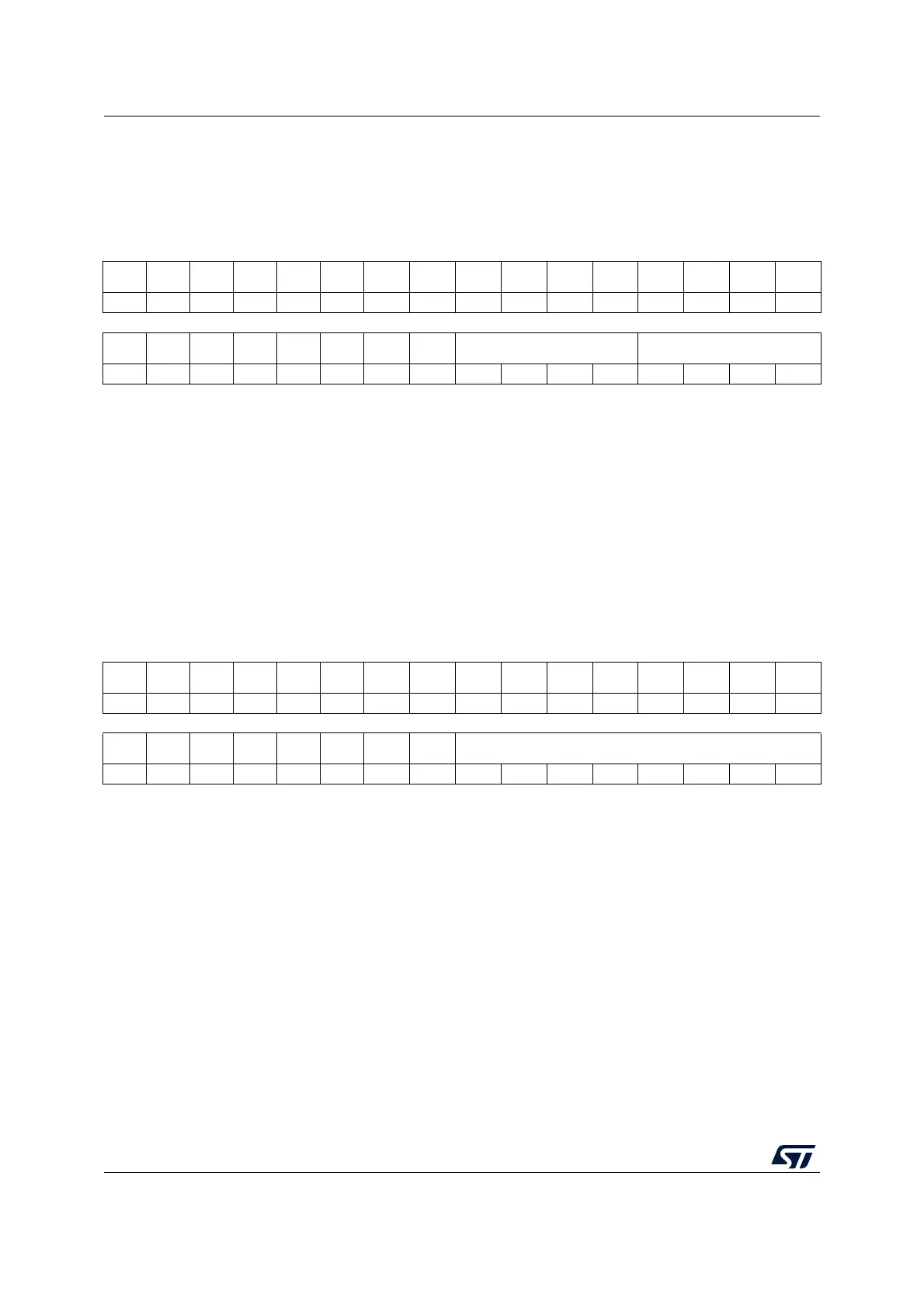

38.8.8 CPU1 ROM CoreSight peripheral identity register 1 (ROM_CIDR1)

Address offset: 0xFF4

Reset value: 0x0000 0010

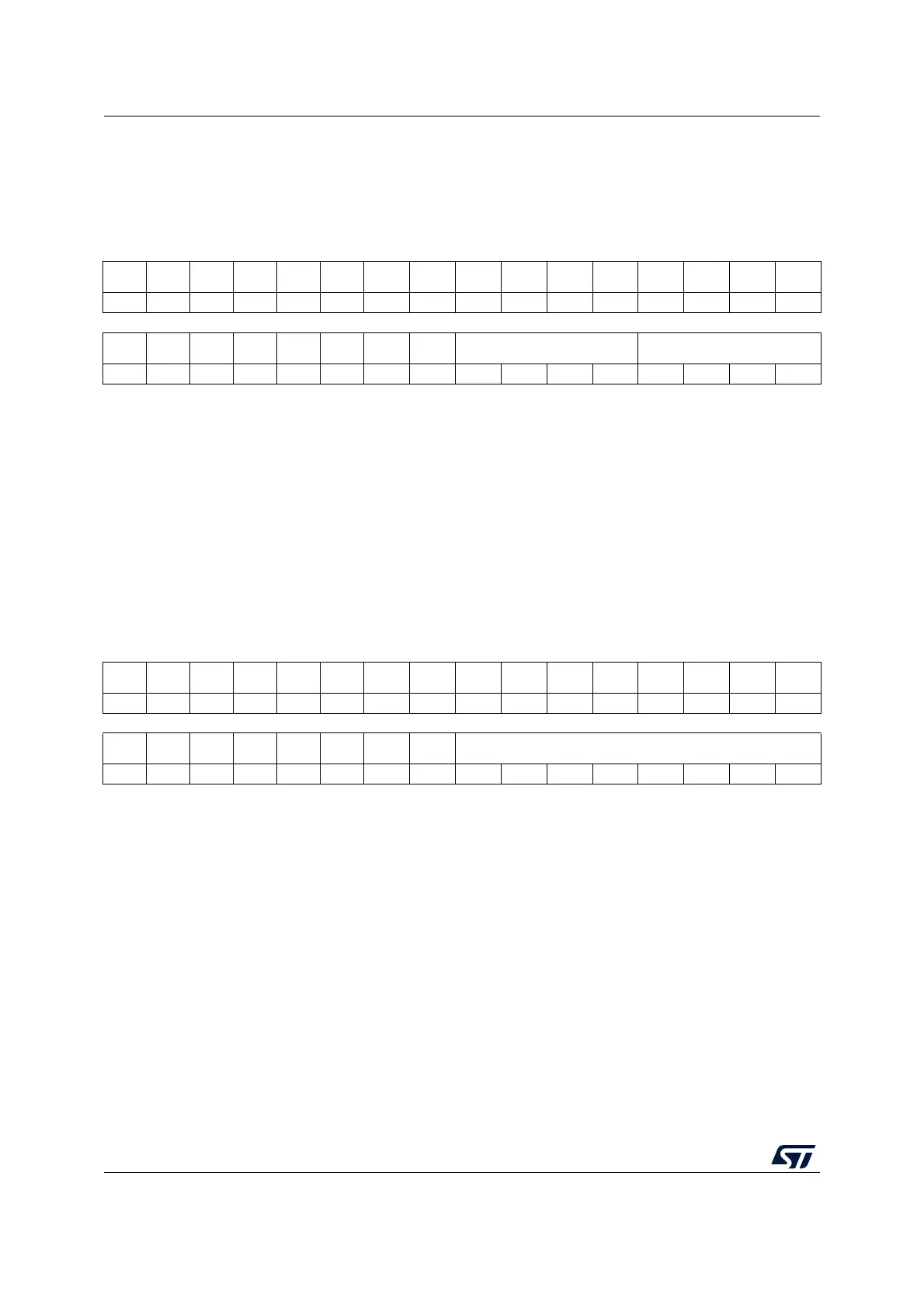

38.8.9 CPU1 ROM CoreSight component identity register 2 (ROM_CIDR2)

Address offset: 0xFF8

Reset value: 0x0000 0005

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. CLASS[3:0] PREAMBLE[11:8]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:4 CLASS[3:0]: component ID bits [15:12] - component class

0x1: ROM table component

Bits 3:0 PREAMBLE[11:8]: component ID bits [11:8]

0x0: Common ID value

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. PREAMBLE[19:12]

rrrrrrrr

Bits 31:8 Reserved, must be kept at reset value.

Bits 7:0 PREAMBLE[19:12]: component ID bits [23:16]

0x05: Common ID value

Loading...

Loading...