RM0453 Rev 1 1407/1461

RM0453 Debug support (DBG)

1448

Refer to Section 38.8: CPU1 ROM table for the register boundary addresses.

38.11 CPU1 trace port interface unit (TPIU)

The TPIU formats the trace stream and outputs it on the external trace port signals. The

TPIU has one ATB slave ports for incoming trace data from the ITM. The trace port is the

serial-wire output, TRACESWO.

Figure 391 shows the TPIU architecture.

0xE04 to

0xE4C

Reserved Reserved.

0xE80

ITM_TCR

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

BUSY

TRACEBUSID[6:0]

Res.

Res.

Res.

Res.

Res.

Res.

TSPRESCALE[1:0]

Res.

Res.

Res.

SWOENA

TXENA

SYNCENA

TSENA

ITMENA

Reset value 00000000 00 00000

0xE84 to

0xFCC

Reserved Reserved.

0xFD0

ITM_PIDR4

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

F4KCOUNT

[3:0]

JEP106CON

[3:0]

Reset value 00000100

0xFD4 to

0xFDC

Reserved Reserved.

0xFE0

ITM_PIDR0

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PARTNUM[7:0]

Reset value 00000001

0xFE4

ITM_PIDR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

JEP106ID

[3:0]

PARTNUM

[11:8]

Reset value 10110000

0xFE8

ITM_PIDR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

REVISION

[3:0]

JEDEC

JEP106ID

[6:4]

Reset value 00111011

0xFEC

ITM_PIDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

REVAND[3:0] CMOD[3:0]

Reset value 00000000

0xFF0

ITM_CIDR0

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[7:0]

Reset value 00001101

0xFF4

ITM_CIDR1

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

CLASS[3:0]

PREAMBLE

[11:8]

Reset value 11100000

0xFF8

ITM_CIDR2

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[19:12]

Reset value 00000101

0xFFC

ITM_CIDR3

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

Res.

PREAMBLE[27:20]

Reset value 10110001

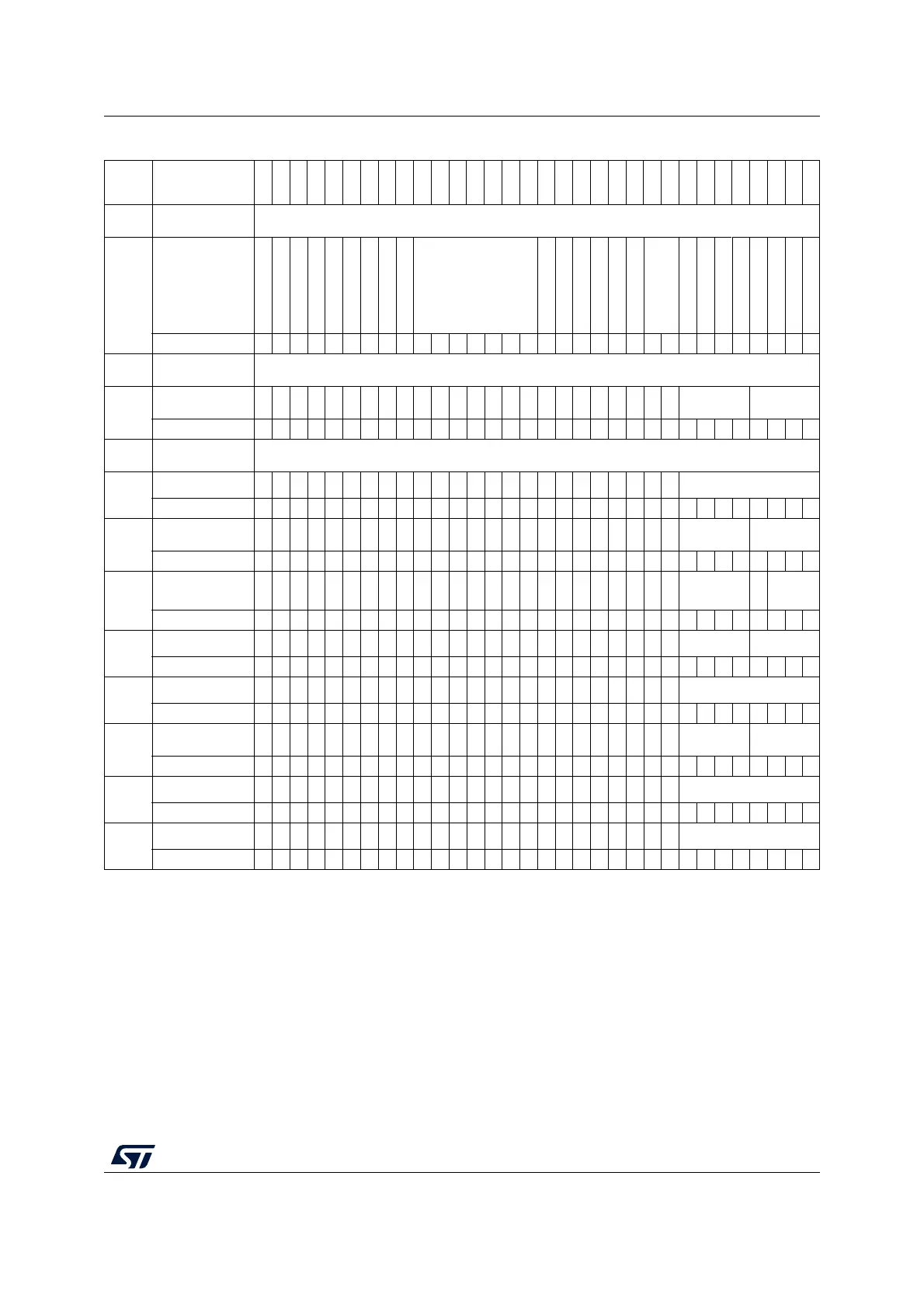

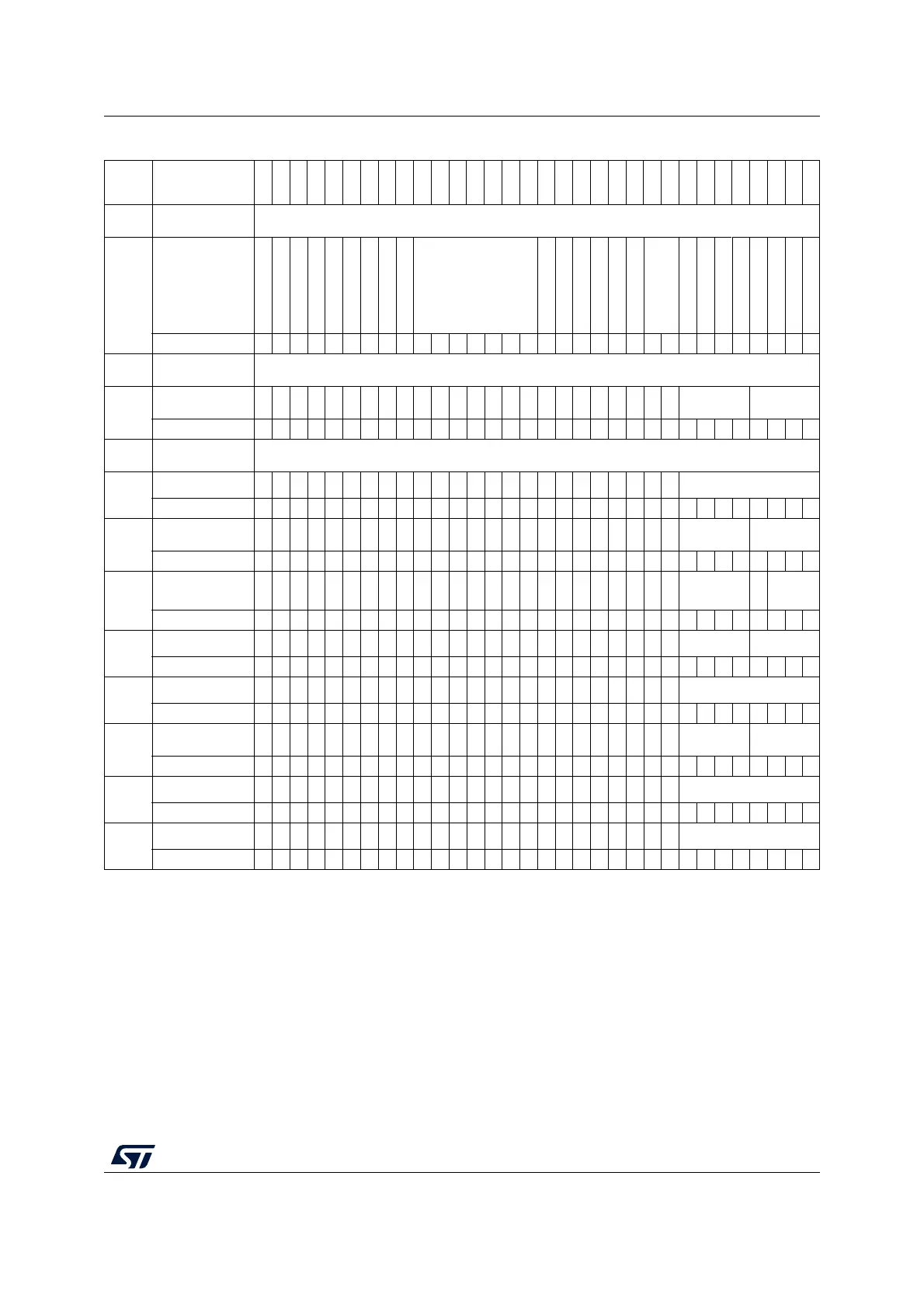

Table 280. CPU1 ITM register map and reset values (continued)

Offset Register name

31

30

29

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

0

Loading...

Loading...