RM0453 Rev 1 1351/1461

RM0453 Debug support (DBG)

1448

A DWT comparator compares the value held in its DWT_COMPxR registers with one of the

following:

• a data address

• an instruction address

• a data value

• the cycle count value, for comparator 0 only.

For address matching, the comparator can use a mask, so it matches a range of addresses.

On a successful match, the comparator generates one of the following:

• one or more DWT data trace packets, containing one or more of:

– the address of the instruction that caused a data access

– an address offset, bits[15:0] of the data access address

– the matched data value

• a watchpoint debug event, on either the PC value or the accessed data address

• a CMPMATCH[N] event that signals the match outside the DWT unit

A watchpoint debug event either generates a DebugMonitor exception or causes the

processor to halt execution and enter Debug state.

For more details on how to use the DWT, refer to the Arm

®

v7-M Architecture Reference

Manual [5].

38.6.1 DWT control register (DWT_CTRLR)

Address offset: 0x000

Reset value: 0x4000 0000

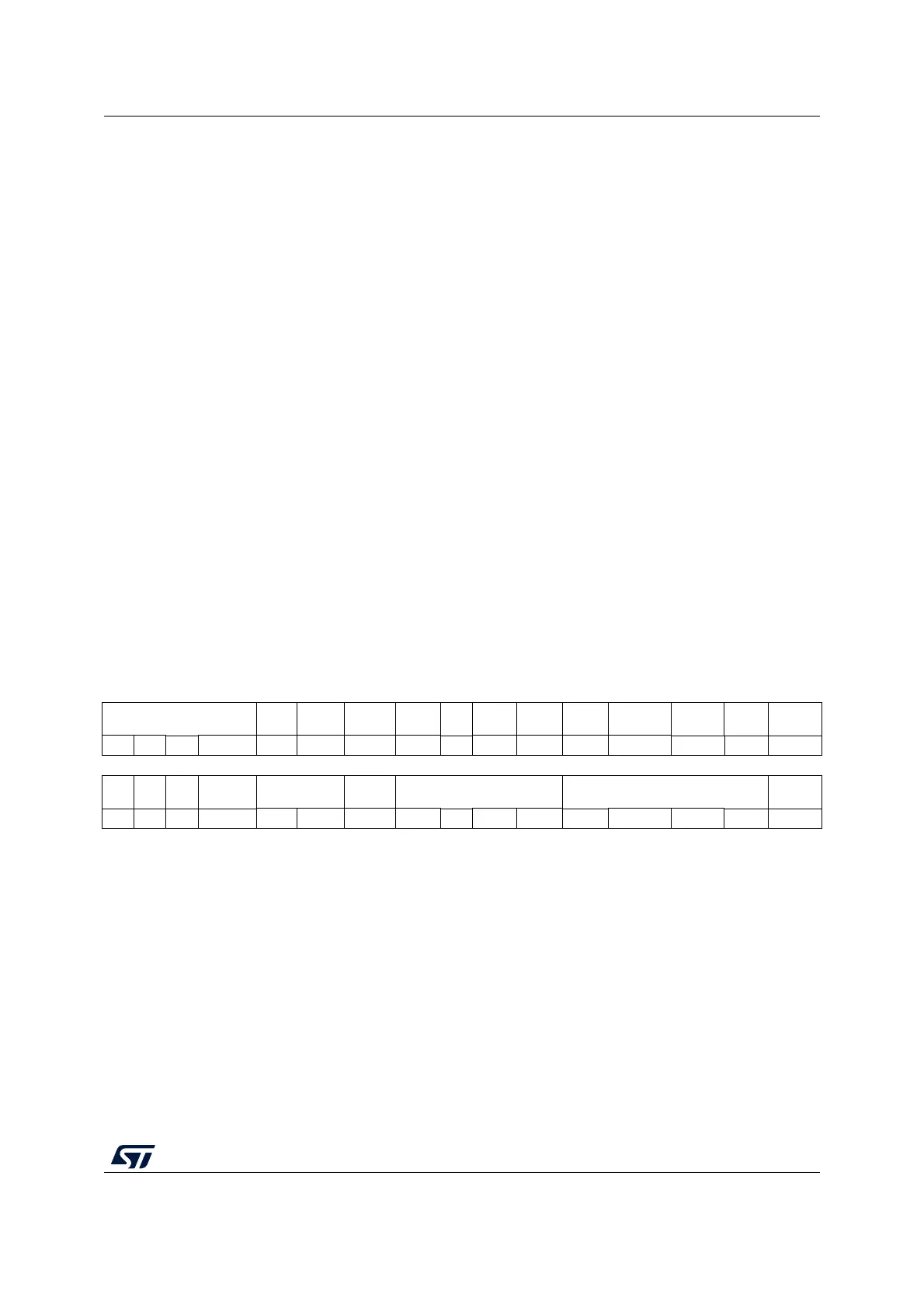

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

NUMCOMP[3:0]

NOTR

CPKT

NOEXT

TRIG

NOCYC

CNT

NOPRF

CNT

Res.

CYCEV

TENA

FOLDE

VTENA

LSUEV

TENA

SLEEPEVT

ENA

EXCEVT

ENA

CPIEV

TENA

EXCTRC

ENA

r r r r r r r r rw rw rw rw rw rw rw

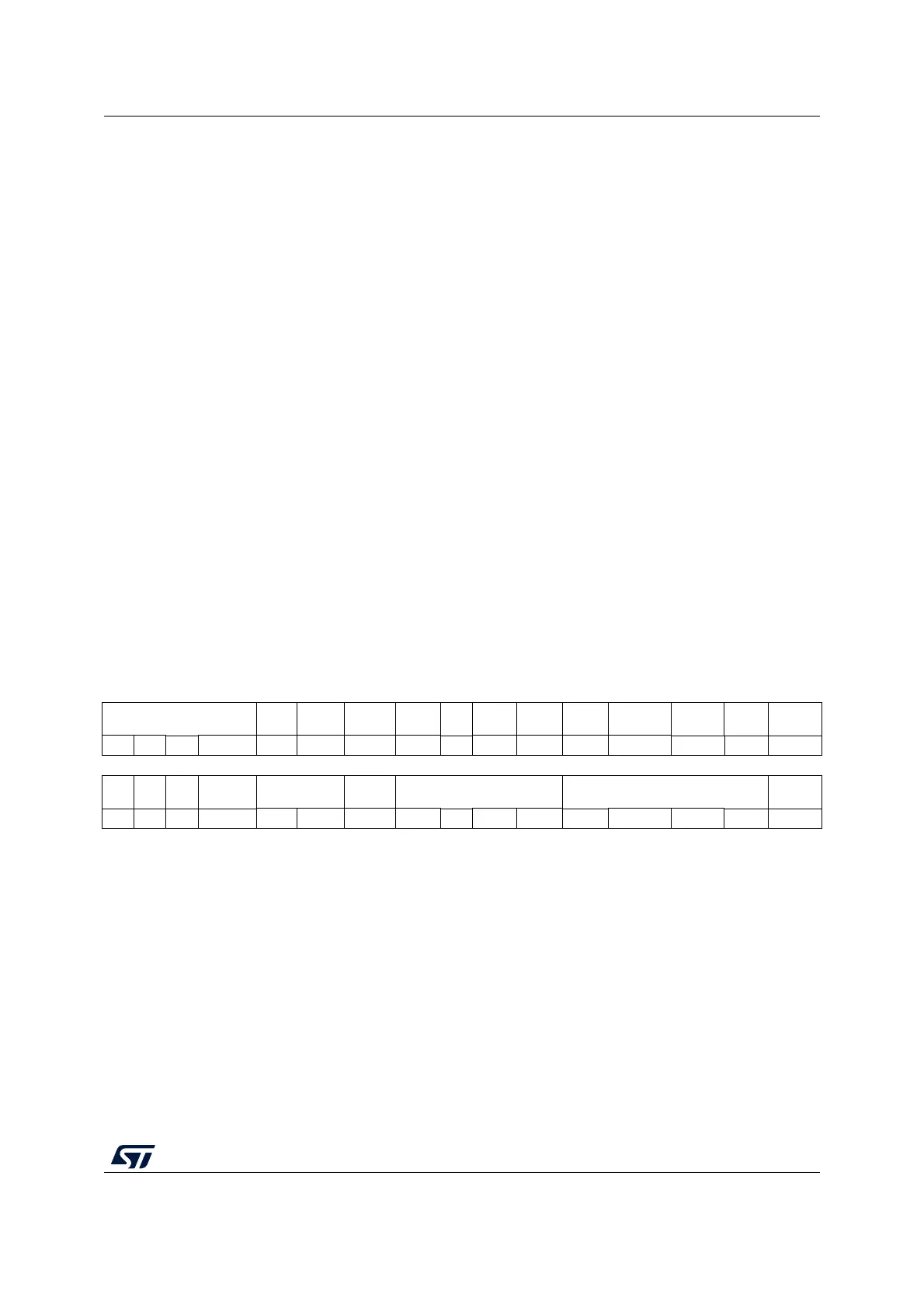

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res.

PCSAMPL

ENA

SYNCTAP[1:0] CYCTAP POSTINIT[3:0] POSTPRESET[3:0]

CYCCNT

ENA

rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:28 NUMCOMP[3:0]: number of comparators implemented (read only)

0x4: Four comparators

Bit 27 NOTRCPKT: trace sampling and exception tracing support (read only)

0: Supported

Bit 26 NOEXTTRIG: external match signal, CMPMATCH support (read only)

0: Supported

Bit 25 NOCYCCNT: cycle counter support (read only)

0: Supported

Bit 24 NOPRFCNT: profiling counter support (read only)

0: Supported

Bit 23 Reserved, must be kept at reset value.

Loading...

Loading...