RM0453 Rev 1 599/1461

RM0453 Digital-to-analog converter (DAC)

618

DMA underrun

The DAC DMA request is not queued so that if a second external trigger arrives before the

acknowledgment for the first external trigger is received (first request), then no new request

is issued and the DMA channel1 underrun flag DMAUDR1 in the DAC_SR register is set,

reporting the error condition. The DAC channel1 continues to convert old data.

The software must clear the DMAUDR1 flag by writing 1, clear the DMAEN bit of the used

DMA stream and re-initialize both DMA and DAC channel1 to restart the transfer correctly.

The software must modify the DAC trigger conversion frequency or lighten the DMA

workload to avoid a new DMA underrun. Finally, the DAC conversion could be resumed by

enabling both DMA data transfer and conversion trigger.

For DAC channel1, an interrupt is also generated if its corresponding DMAUDRIE1 bit in the

DAC_CR register is enabled.

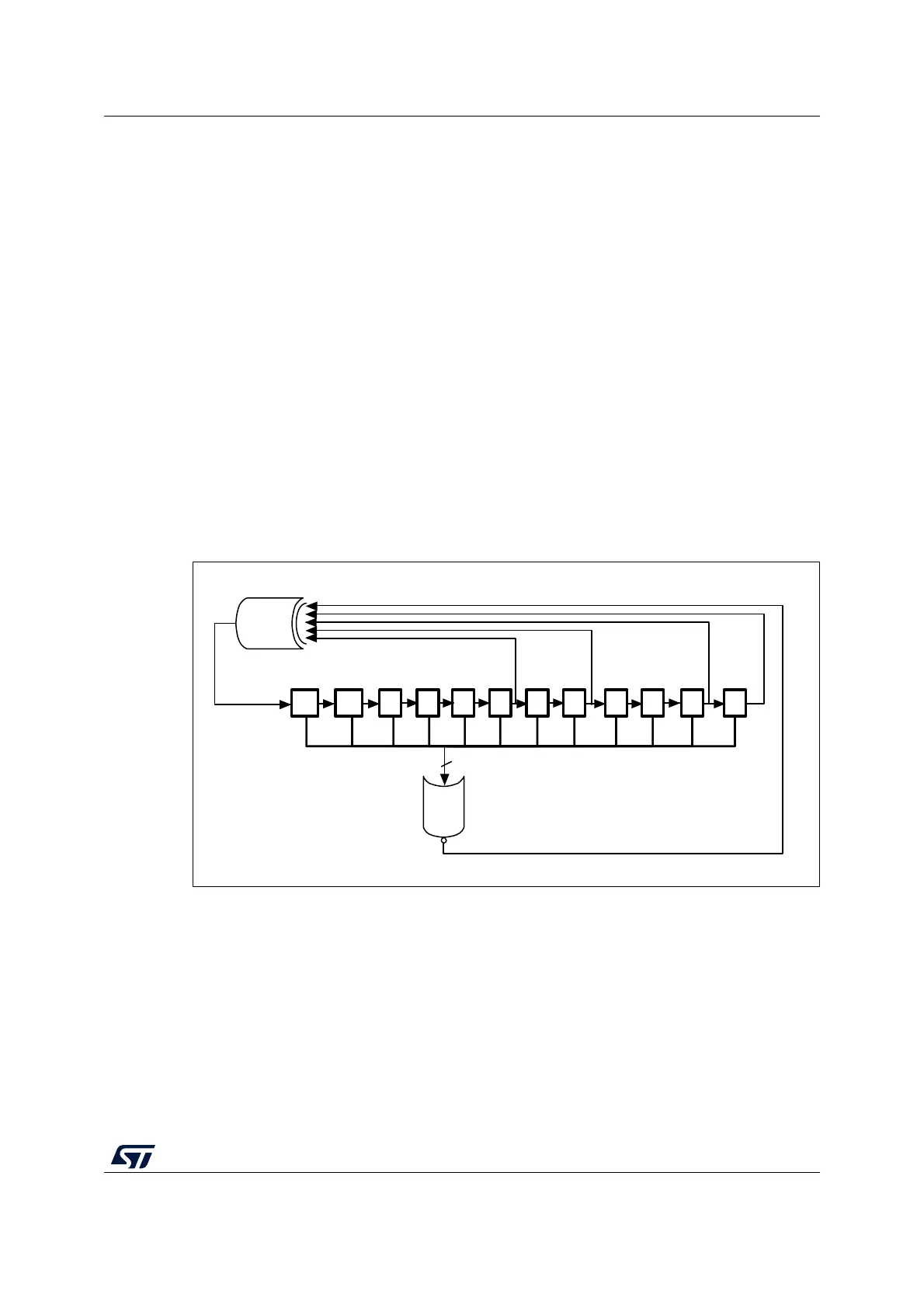

19.4.9 Noise generation

In order to generate a variable-amplitude pseudonoise, an LFSR (linear feedback shift

register) is available. DAC noise generation is selected by setting WAVE1[1:0] to 01. The

preloaded value in LFSR is 0xAAA. This register is updated three dac_pclk clock cycles

after each trigger event, following a specific calculation algorithm.

Figure 89. DAC LFSR register calculation algorithm

The LFSR value, that may be masked partially or totally by means of the MAMP1[3:0] bits in

the DAC_CR register, is added up to the DAC_DHR1 contents without overflow and this

value is then transferred into the DAC_DOR1 register.

If LFSR is 0x0000, a ‘1 is injected into it (antilock-up mechanism).

It is possible to reset LFSR wave generation by resetting the WAVE1[1:0] bits.

11 10 9 8 7 6 5 4 3 2 1 0

12

NOR

X

12

X

0

X

X

4

X

6

XOR

ai14713c