RM0453 Rev 1 1347/1461

RM0453 Debug support (DBG)

1448

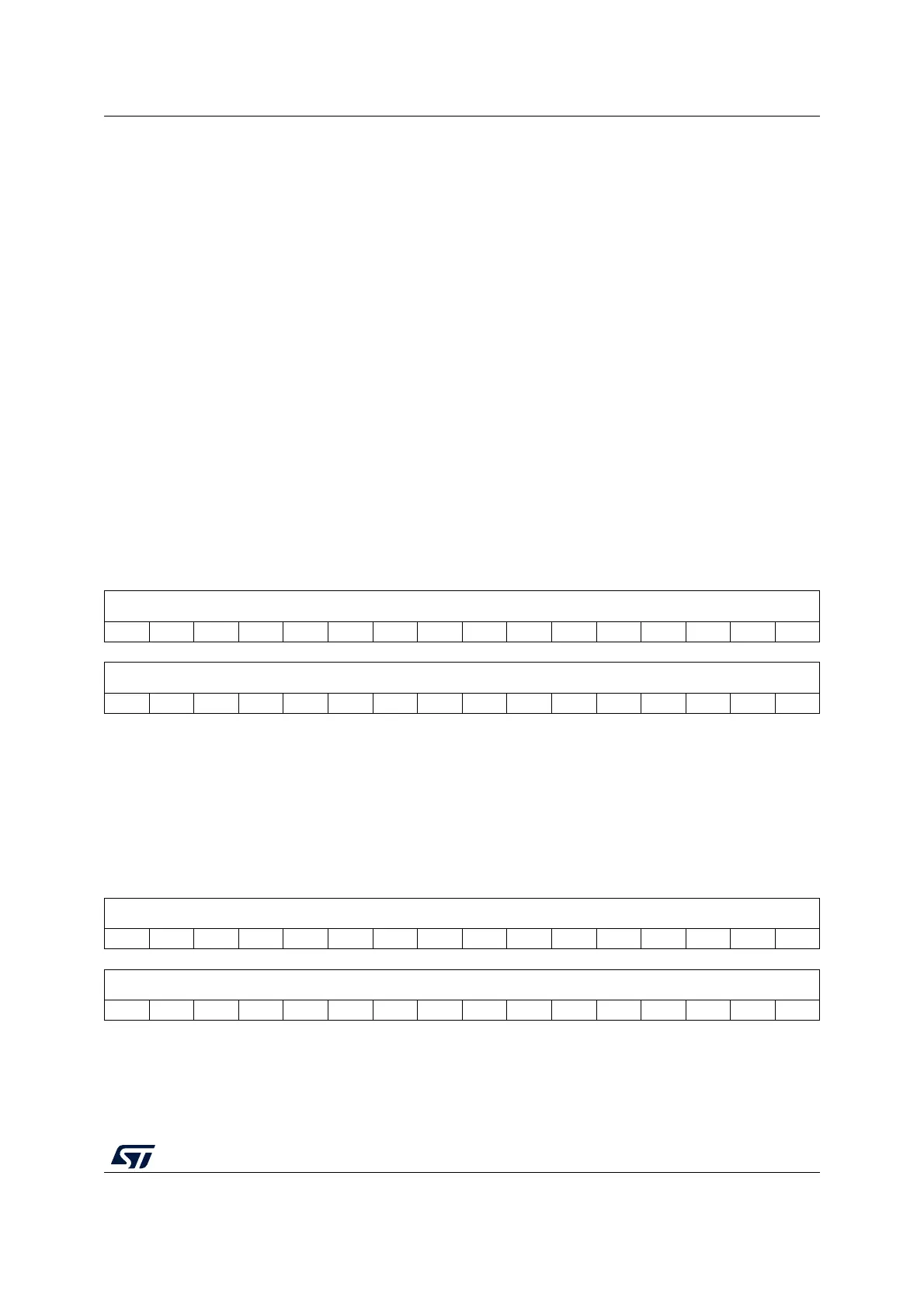

38.5.2 AP transfer address register (AP_TAR)

Address offset: 0x04

Reset value: 0x0000 0000

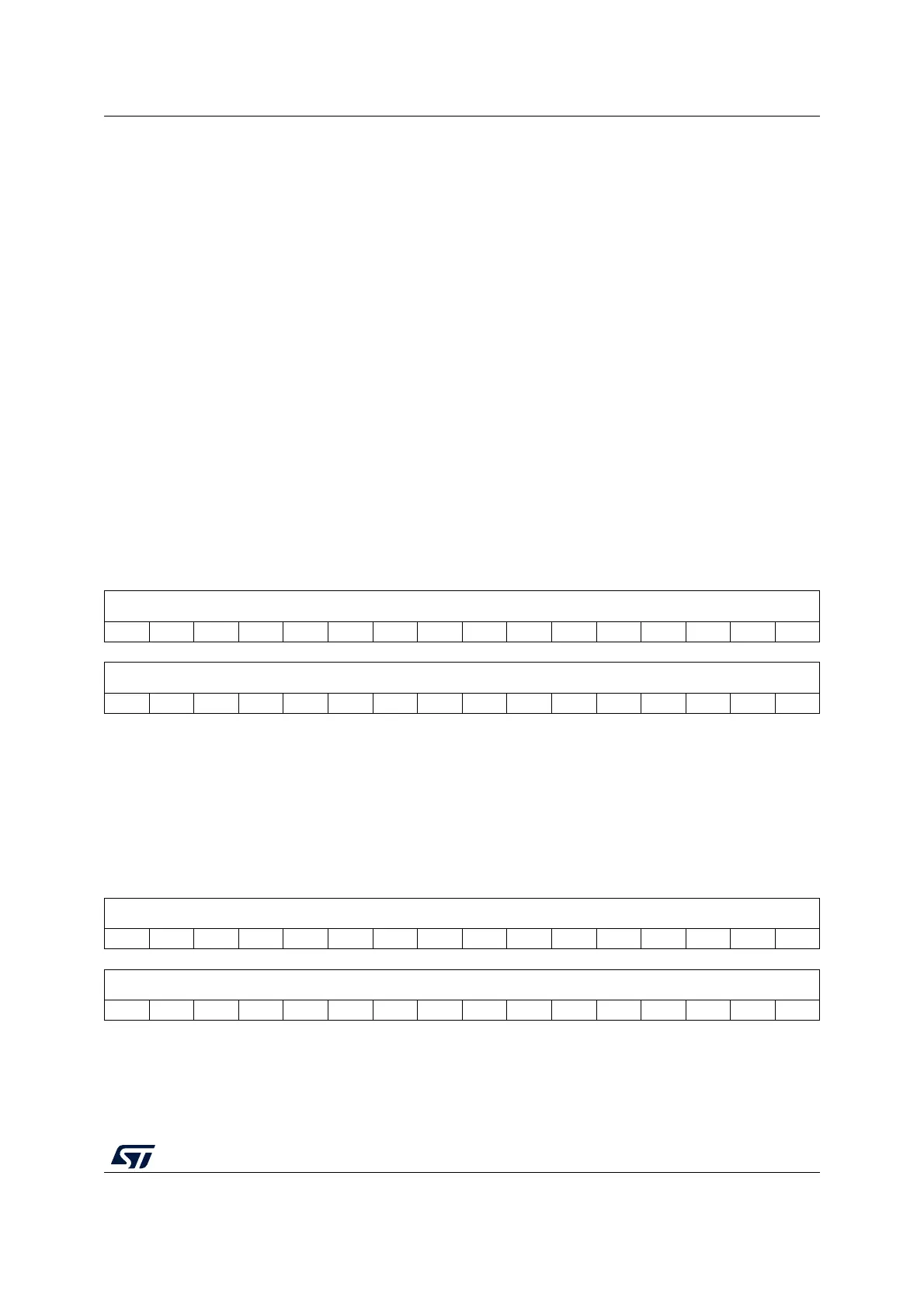

38.5.3 AP data read/write register (AP_DRWR)

Address offset: 0x0C

Reset value: 0x0000 0000

Bits 5:4 ADDRINC[1:0]: auto-increment mode

Defines whether AP_TAR address is automatically incremented after a transaction.

0x0: No auto-increment

0x1: Address is incremented by the size in bytes of the transaction (SIZE field).

0x2: Packed transfers enabled

– A 32-bit AP access gives rise to 1 x 32-bit, 2 x 16-bit or 4 x 8-bit bus transactions

corresponding to the programmed transaction size.

– The data is packed or unpacked accordingly.

0x3: reserved

Bit 3 Reserved, must be kept at reset value.

Bits 2:0 SIZE[2:0]: size of next memory access transaction

0x0: Byte (8-bit)

0x1: Halfword (16-bit)

0x2: Word (32-bit)

0x3-0x7: reserved

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TA[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

TA[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 TA[31:0]: address of current transfer

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

TD[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

TD[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 TD[31:0]: data of current transfer

Loading...

Loading...