Power control (PWR) RM0453

236/1461 RM0453 Rev 1

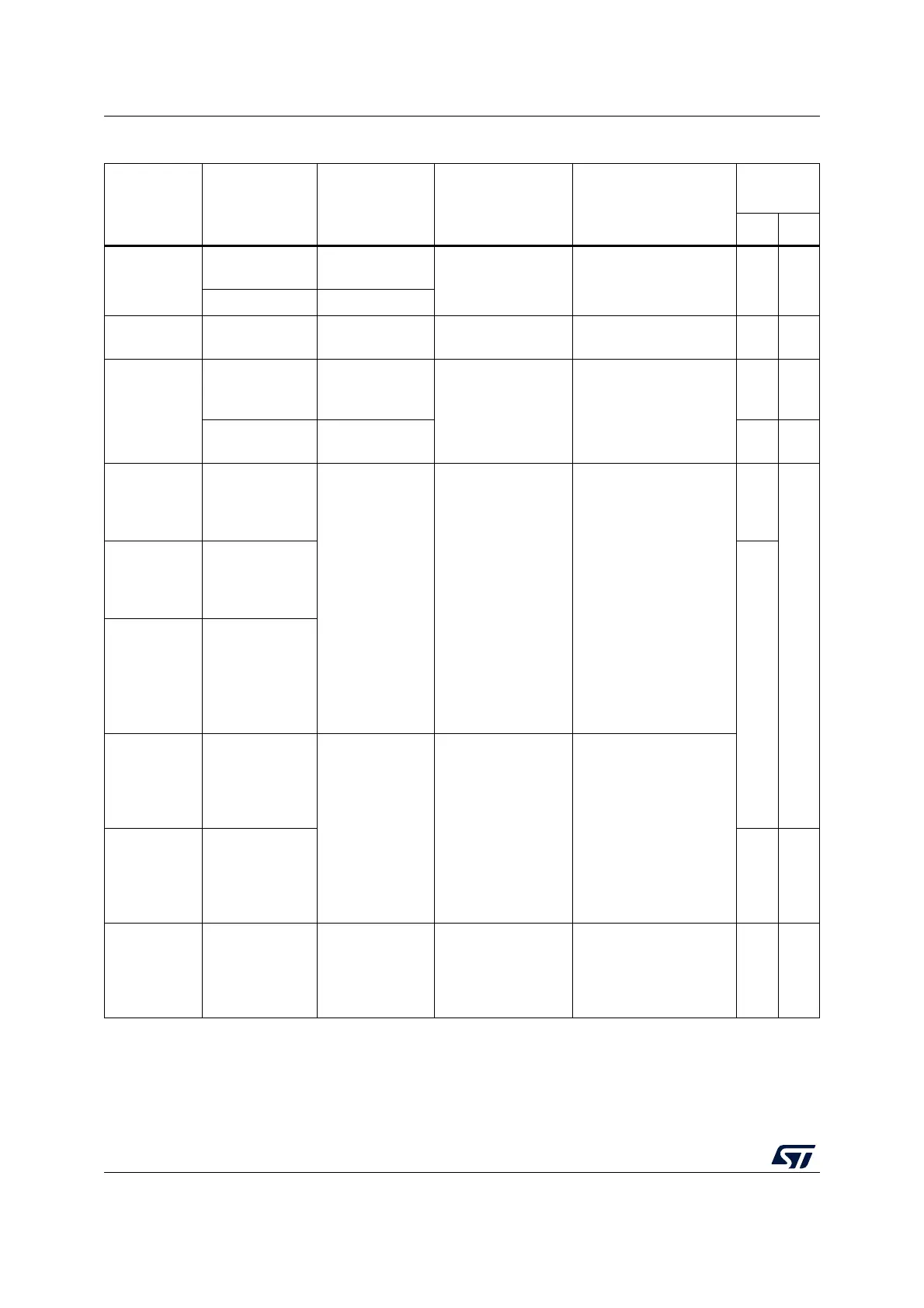

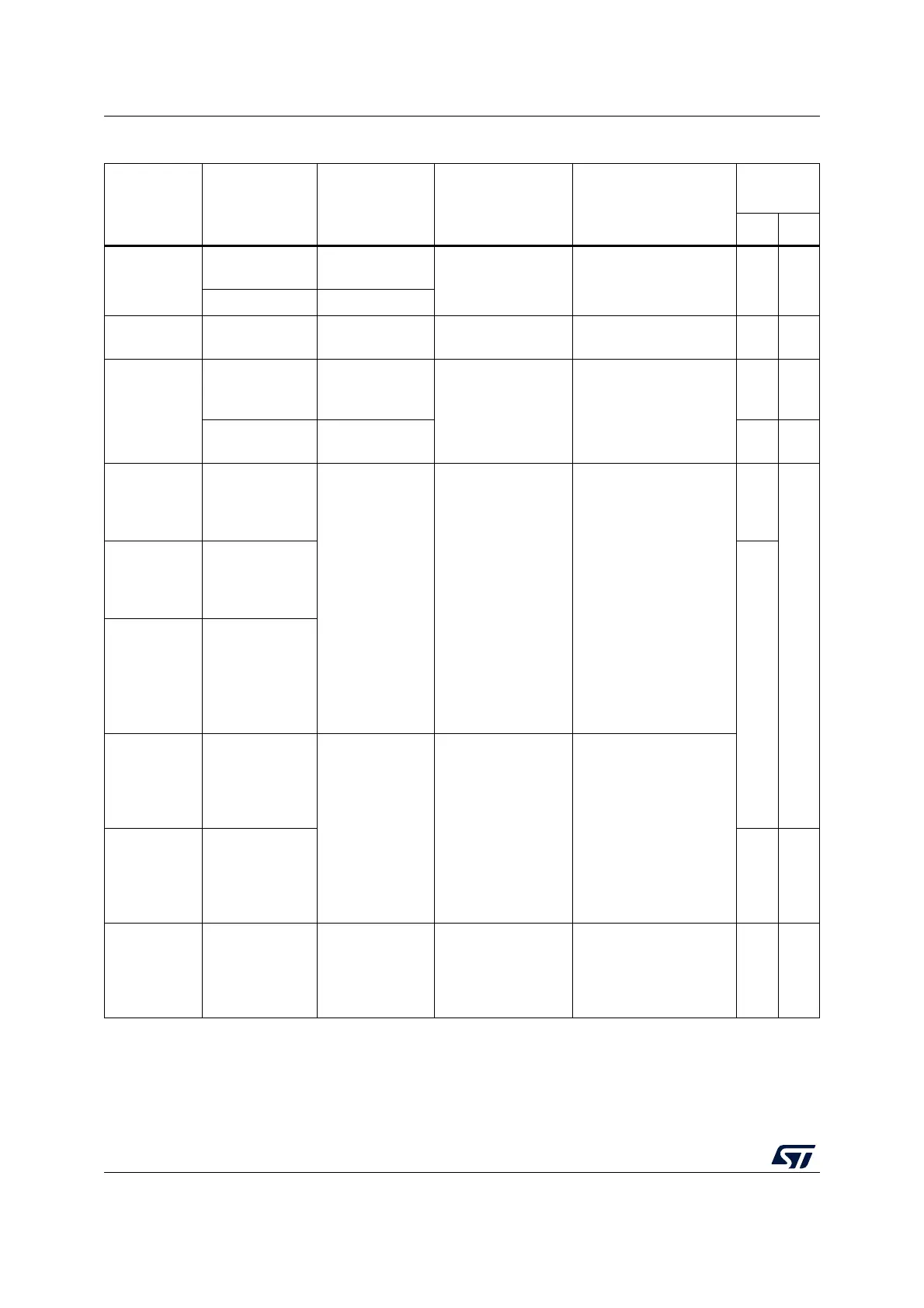

Table 44. Low-power mode summary

Mode name Entry

Wakeup

source

(1)

Wakeup

system clock

Effect on clocks

Voltage

regulators

MR LPR

Sleep

(Sleep-now or

Sleep-on-exit)

WFI or return

from ISR

Any interrupt

Same as before

entering Sleep mode

CPU clock OFF

No effect on other clocks

or analog clock sources

ON ON

WFE Wakeup event

LPRun Set LPR bit Clear LPR bit

Same as LPRun

clock

None OFF ON

LPSleep

Set LPR bit +

WFI or return

from ISR

Any interrupt

Same as before

entering LPSleep

mode

CPU clock OFF

No effect on other clocks

or analog clock sources

OFF ON

Set LPR bit +

WFE

Wakeup event OFF ON

Stop 0

LPMS = 0b000 +

SLEEPDEEP bit

+ WFI or return

from ISR or WFE

Any EXTI line

(configured in the

EXTI registers).

Specific

peripherals

events

HSI16 when

STOPWUCK = 1 in

RCC_CFGR.

MSI with the

frequency before

entering the Stop

mode when

STOPWUCK = 0.

All clocks OFF

except HSI16, LSI and

LSE

ON

ON

Stop 1

LPMS = 0b001 +

SLEEPDEEP bit

+ WFI or return

from ISR or WFE

OFF

Stop 2

(with I2C3,

LPUART1,

LPTIM1,

SRAM1,

SRAM2)

LPMS = 0b010+

SLEEPDEEP bit

+ WFI or return

from ISR or WFE

Standby (with

SRAM2)

LPMS = 0b011+

Set RRS bit +

SLEEPDEEP bit

+ WFI or return

from ISR or WFE

Wakeup PVD,

RFIRQ, wakeup

RFBUSY, WKUP

pin edge, RTC

and TAMP event,

LSECSS,

external reset in

NRST pin,

IWDG reset

MSI 4 MHz

All clocks OFF

except LSI and LSE

Standby

LPMS = 0b011 +

Clear RRS bit +

SLEEPDEEP bit

+ WFI or return

from ISR or WFE

OFF OFF

Shutdown

LPMS = 0b1xx +

SLEEPDEEP bit

+ WFI or return

from ISR or WFE

WKUP pin edge,

RTC and TAMP

event, external

reset in NRST

pin

MSI 4 MHz

All clocks OFF

except LSE

OFF OFF

1. Refer to Table 45: Functionalities depending on system operating mode.

Loading...

Loading...