Analog-to-digital converter (ADC) RM0453

572/1461 RM0453 Rev 1

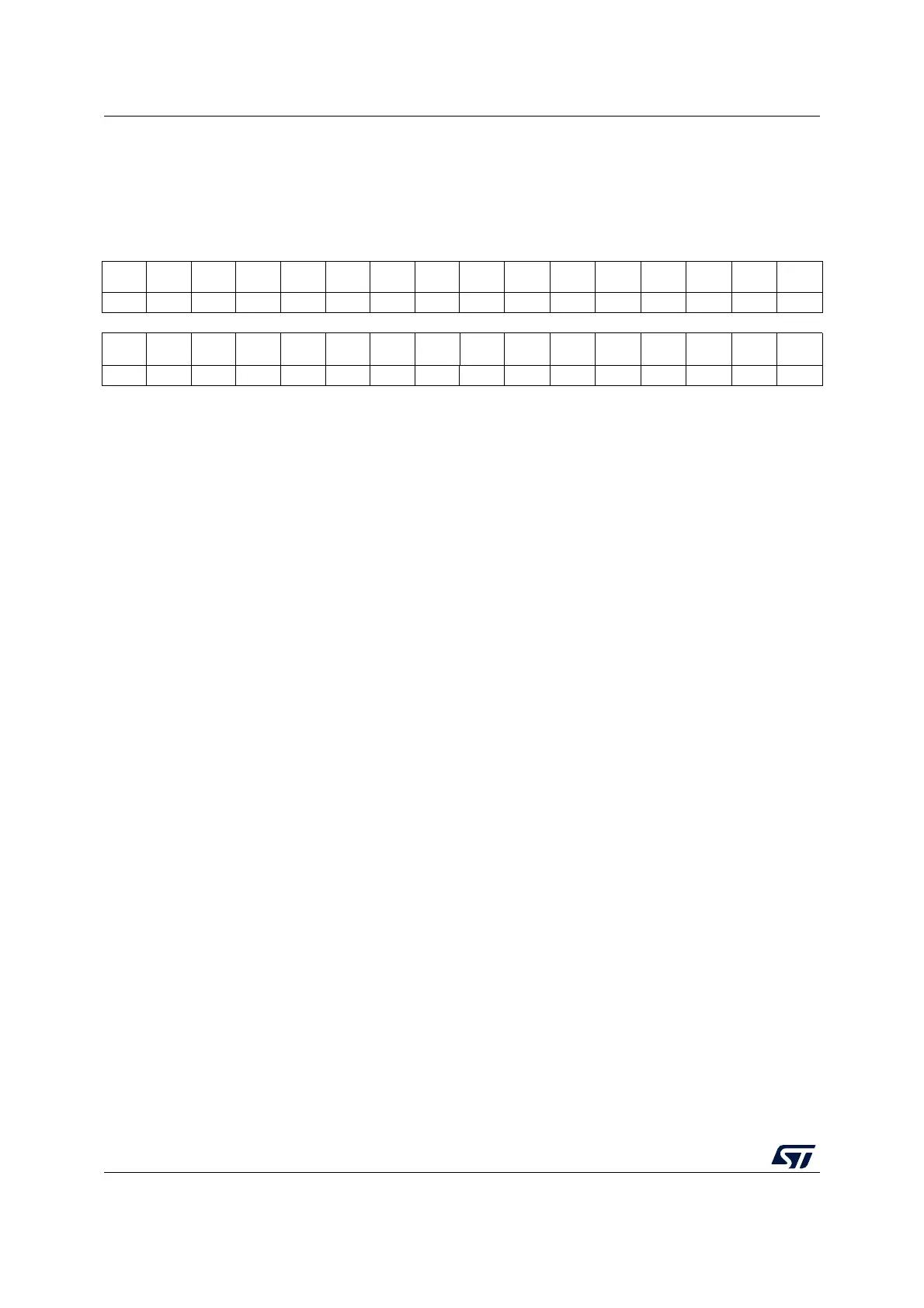

18.12.2 ADC interrupt enable register (ADC_IER)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res.

CCRD

YIE

Res.

EOCAL

IE

Res.

AWD3I

E

AWD2I

E

AWD1I

E

Res. Res. OVRIE EOSIE EOCIE

EOSMP

IE

ADRDY

IE

rw rw rw rw rw rw rw rw rw rw

Bits 31:14 Reserved, must be kept at reset value.

Bit 13 CCRDYIE: Channel Configuration Ready Interrupt enable

This bit is set and cleared by software to enable/disable the channel configuration ready interrupt.

0: Channel configuration ready interrupt disabled

1: Channel configuration ready interrupt enabled

Note: The software is allowed to write this bit only when ADSTART bit is cleared to 0 (this ensures

that no conversion is ongoing).

Bit 12 Reserved, must be kept at reset value.

Bit 11 EOCALIE: End of calibration interrupt enable

This bit is set and cleared by software to enable/disable the end of calibration interrupt.

0: End of calibration interrupt disabled

1: End of calibration interrupt enabled

Note: The software is allowed to write this bit only when ADSTART bit is cleared to 0 (this ensures

that no conversion is ongoing).

Bit 10 Reserved, must be kept at reset value.

Bit 9 AWD3IE: Analog watchdog 3 interrupt enable

This bit is set and cleared by software to enable/disable the analog watchdog interrupt.

0: Analog watchdog interrupt disabled

1: Analog watchdog interrupt enabled

Note: The Software is allowed to write this bit only when ADSTART bit is cleared to 0 (this ensures

that no conversion is ongoing).

Bit 8 AWD2IE: Analog watchdog 2 interrupt enable

This bit is set and cleared by software to enable/disable the analog watchdog interrupt.

0: Analog watchdog interrupt disabled

1: Analog watchdog interrupt enabled

Note: The Software is allowed to write this bit only when ADSTART bit is cleared to 0 (this ensures

that no conversion is ongoing).

Bit 7 AWD1IE: Analog watchdog 1 interrupt enable

This bit is set and cleared by software to enable/disable the analog watchdog interrupt.

0: Analog watchdog interrupt disabled

1: Analog watchdog interrupt enabled

Note: The Software is allowed to write this bit only when ADSTART bit is cleared to 0 (this ensures

that no conversion is ongoing).

Bits 6:5 Reserved, must be kept at reset value.

Loading...

Loading...