RM0453 Rev 1 1429/1461

RM0453 Debug support (DBG)

1448

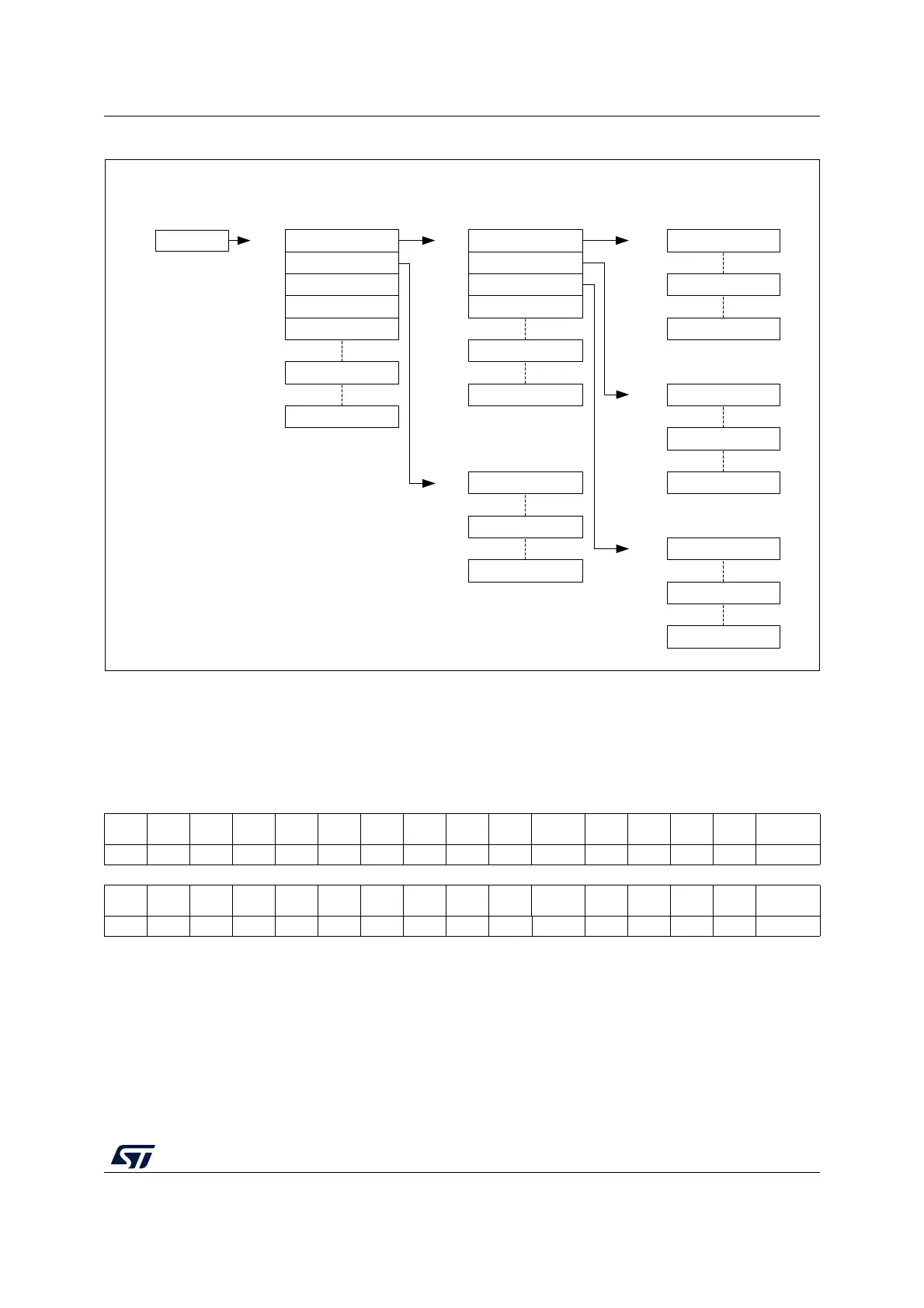

Figure 392. CPU2 CoreSight topology

38.13.1 CPU2 ROM1 memory type register (C2ROM1_MEMTYPER)

Address offset: 0xFCC

Reset value: 0x0000 0001

MSv60372V1

0x004

0xFD0

0xFFC

0x008

0x008

0x00C

Register file base

System control space (SCS)

@0xE000E000

0x000

PIDR40xFD0

CIDR30xFFC

Register file base

Data watchpoint/trace (DWT)

@0xE0001000

0x000

PIDR40xFD0

CIDR30xFFC

Register file base

Breakpoint Unit (BPU)

@0xE0002000

0x000

PIDR40xFD0

CIDR30xFFC

0xF0000000

AP1

(AHB-AP)

AP_BASER register

(0xF8)

CPU2 ROM1 table

@0xF0000000

Top of table

PIDR4

CIDR3

Offset: 0x00001000

Offset: 0x00002000

Offset: 0x10000000

CPU2 ROM2 table

@0xE00FF000

0x000

Top of table

0x004

0x008

0x00C

Register file base0x000

PIDR40xFD0

CIDR30xFFC

Cross trigger interface (CTI)

@0xF0001000

PIDR40xFD0

CIDR30xFFC

Offset: 0xFFF0F000

Offset: 0xFFF02000

Offset: 0xFFF03000

0x000

Offset: 0xF00FF000

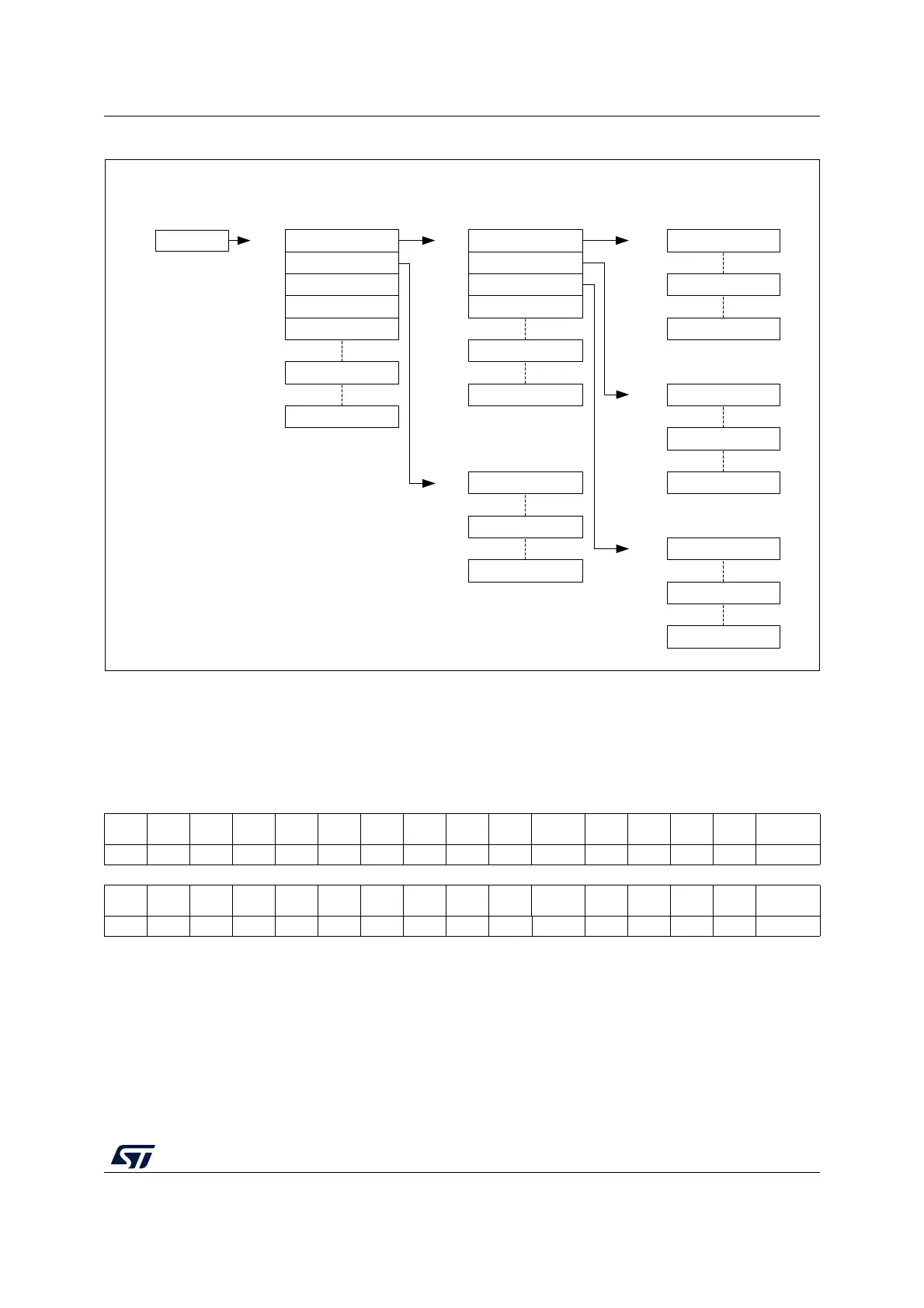

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. SYSMEM

r

Bits 31:1 Reserved, must be kept at reset value.

Bit 0 SYSMEM: system memory

1: System memory present on this bus

Loading...

Loading...