RM0453 Rev 1 263/1461

RM0453 Power control (PWR)

276

6.6.7 PWR status clear register (PWR_SCR)

Access: three additional APB cycles are needed to write this register versus a standard APB

write.

Address offset: 0x018

Reset value: 0x0000 0000

Bit 2 RFBUSYMS: Radio busy masked signal status

This bit indicates the actual status of the radio busy masked signal.

0: radio busy masked signal low (not busy)

1: radio busy masked signal high (busy)

Bit 1 RFBUSYS: Radio busy signal status

This bit indicates the actual status of the radio busy signal.

0: radio busy signal low (not busy)

1: radio busy signal high (busy)

Bit 0 C2BOOTS: CPU2 boot/wakeup request source information

This bit indicates the CPU2 boot/wakeup request source.

0: CPU2 booted from an illegal access event

1: CPU2 booted from a C2BOOT request

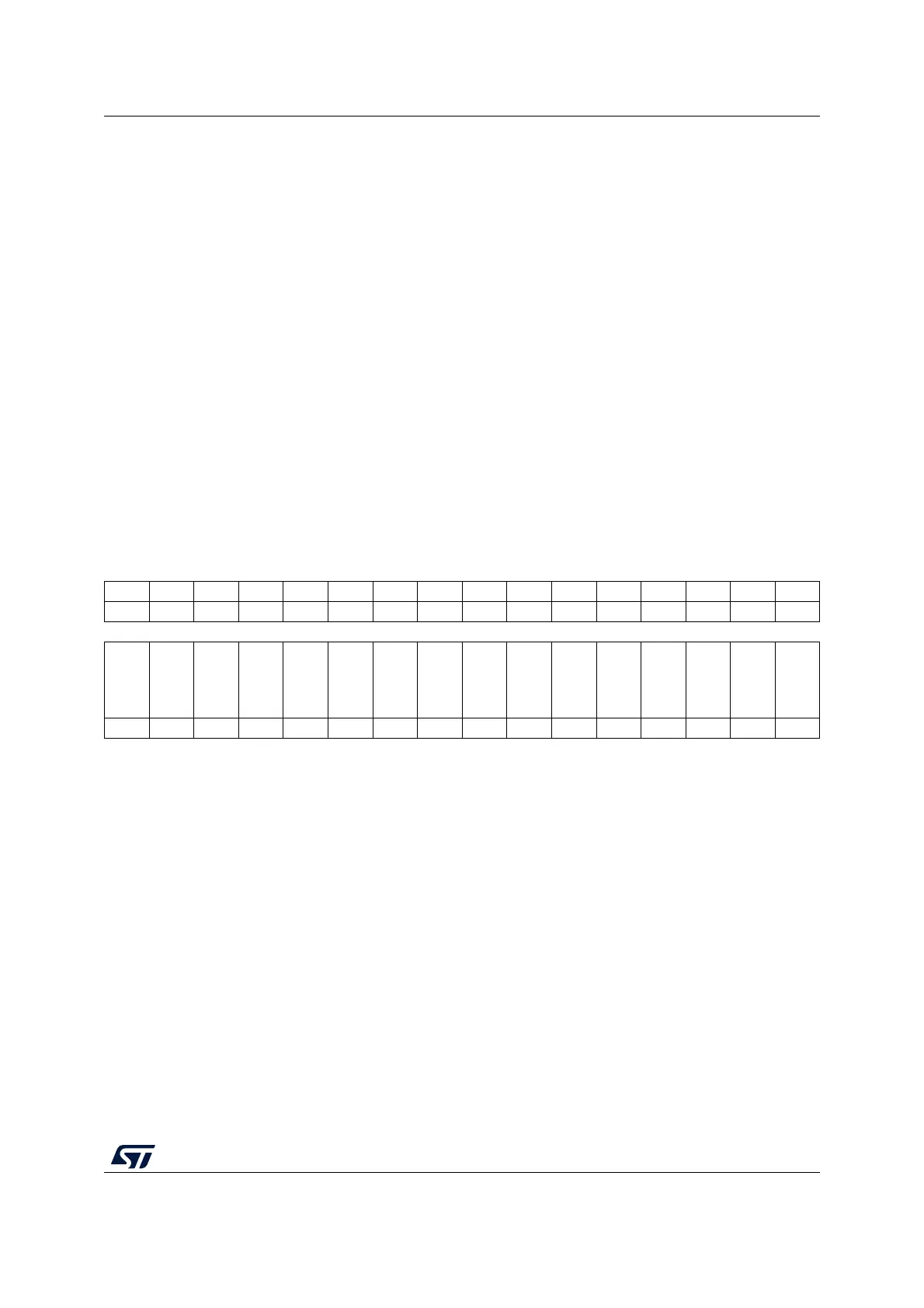

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res.

CC2HF

Res. Res.

CWRFBUSYF

Res. Res.

CWPVDF

Res. Res. Res. Res. Res.

CWUF3

CWUF2

CWUF1

w w w www

Bits 31:15 Reserved, must be kept at reset value.

Bit 14 CC2HF: Clear CPU2 hold interrupt flag

Setting this bit clears the C2HF flag in the PWR_SR1. This bit is always read 0.

Bits 13:12 Reserved, must be kept at reset value.

Bit 11 CWRFBUSYF: Clear wakeup radio busy flag

Setting this bit clears the WRFBUSYF flag in the PWR_SR1. This bit is always read 0.

Bits 10:9 Reserved, must be kept at reset value.

Bit 8 CWPVDF: Clear wakeup PVD interrupt flag

Setting this bit clears the WPVDF flag in the PWR_SR1. This bit is always read as 0.

Bits 7:3 Reserved, must be kept at reset value.

Loading...

Loading...