AES hardware accelerator (AES) RM0453

692/1461 RM0453 Rev 1

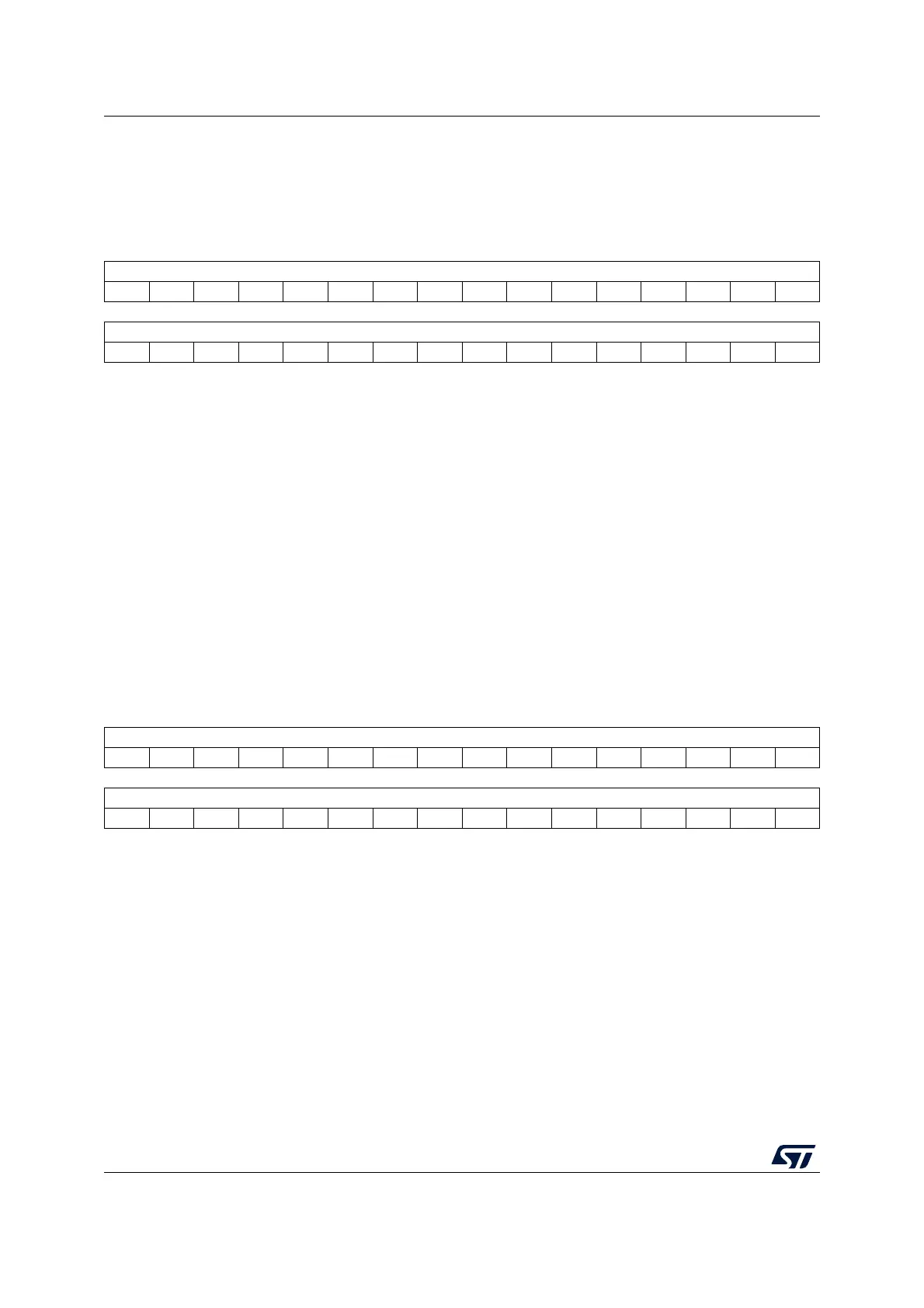

23.7.5 AES key register 0 (AES_KEYR0)

Address offset: 0x10

Reset value: 0x0000 0000

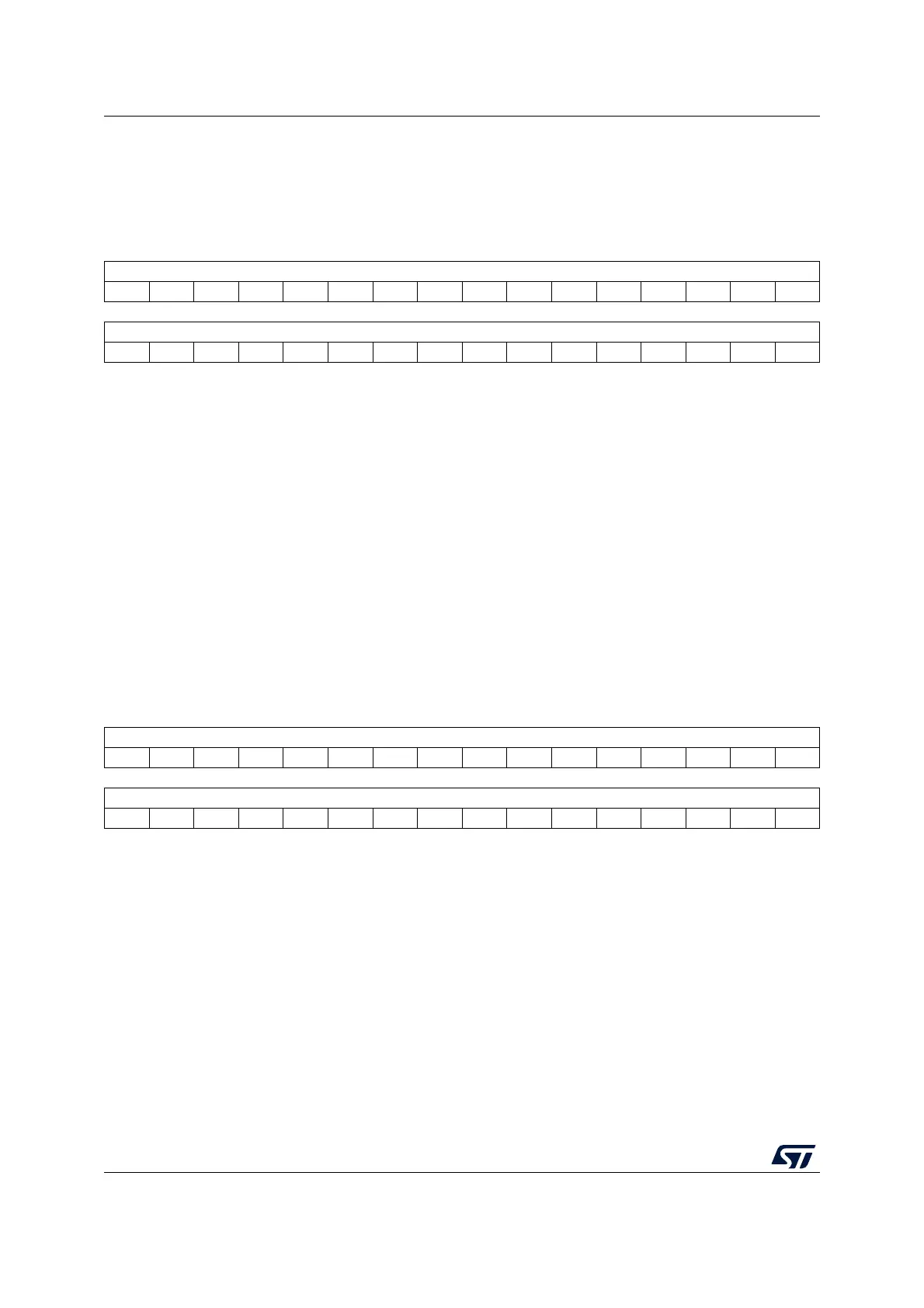

23.7.6 AES key register 1 (AES_KEYR1)

Address offset: 0x14

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEY[31:16]

wwwwwwwwwwwwwwww

1514131211109876543210

KEY[15:0]

wwwwwwwwwwwwwwww

Bits 31:0 KEY[31:0]: Cryptographic key, bits [31:0]

This write-only bitfield contains the bits [31:0] of the AES encryption or decryption key, depending on

the operating mode:

- In Mode 1 (encryption), Mode 2 (key derivation): the value to write into the bitfield is the encryption

key.

- In Mode 3 (decryption): the value to write into the bitfield is the encryption key to be derived before

being used for decryption.

The AES_KEYRx registers may be written only when KEYSIZE value is correct and when the AES

peripheral is disabled (EN bit of the AES_CR register cleared). Note that, if, the key is directly

loaded to AES_KEYRx registers (hence writes to key register is ignored and KEIF is set).

Refer to Section 23.4.14: AES key registers on page 683 for more details.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

KEY[63:48]

wwwwwwwwwwwwwwww

1514131211109876543210

KEY[47:32]

wwwwwwwwwwwwwwww

Bits 31:0 KEY[63:32]: Cryptographic key, bits [63:32]

Refer to the AES_KEYR0 register for description of the KEY[255:0] bitfield.

Loading...

Loading...