RM0453 Rev 1 493/1461

RM0453 DMA request multiplexer (DMAMUX)

498

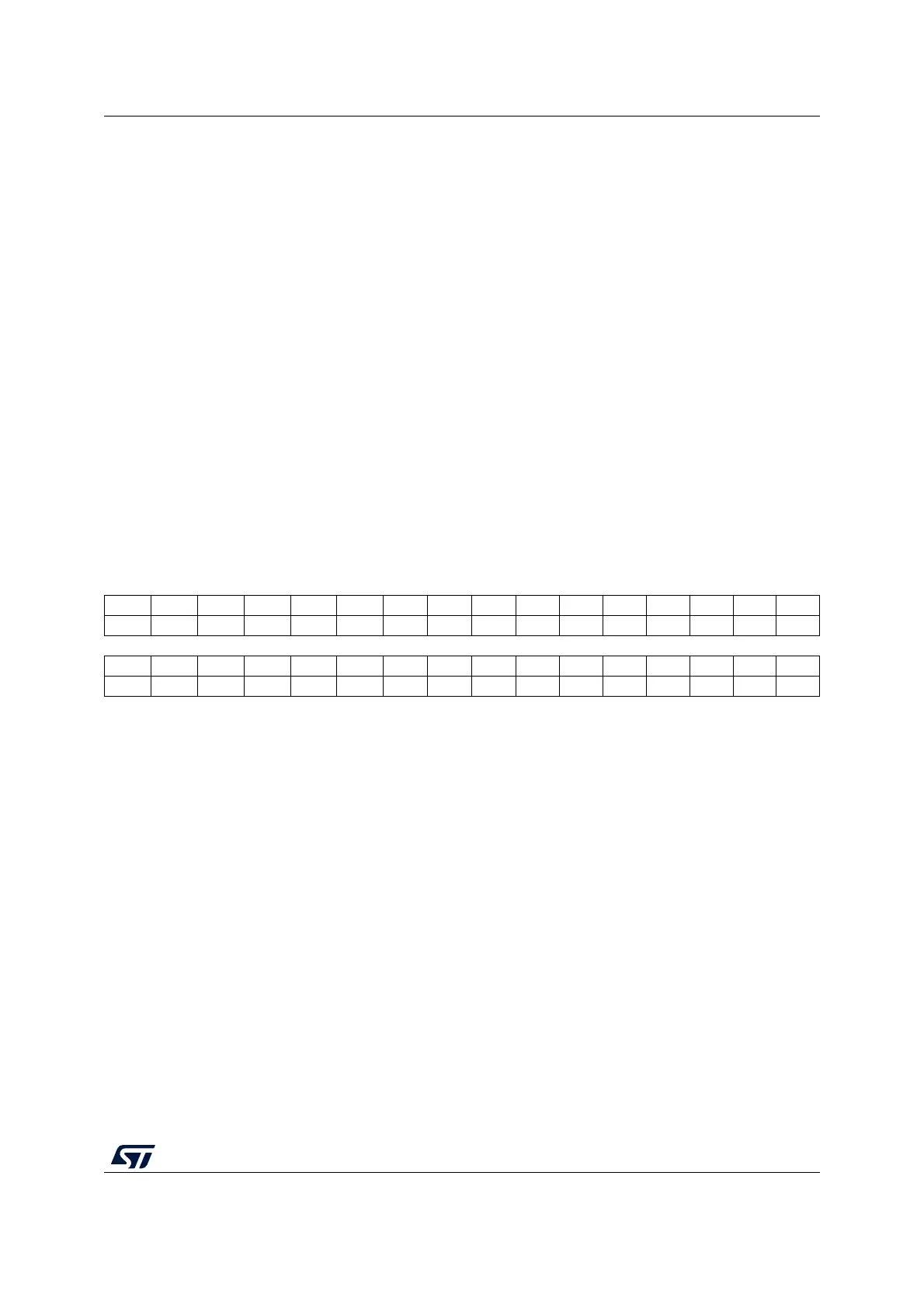

14.6.2 DMAMUX request line multiplexer interrupt channel status register

(DMAMUX_CSR)

Address offset: 0x080

Reset value: 0x0000 0000

This register must be accessed at bit level by a non-secure or secure read, according to the

secure mode of the considered DMAMUX request line multiplexer channel x, depending on

the secure mode bit of the connected DMA controller channel y, and considering that the

DMAMUX x channel output is connected to the y channel of the DMA (refer to the DMAMUX

mapping implementation section).

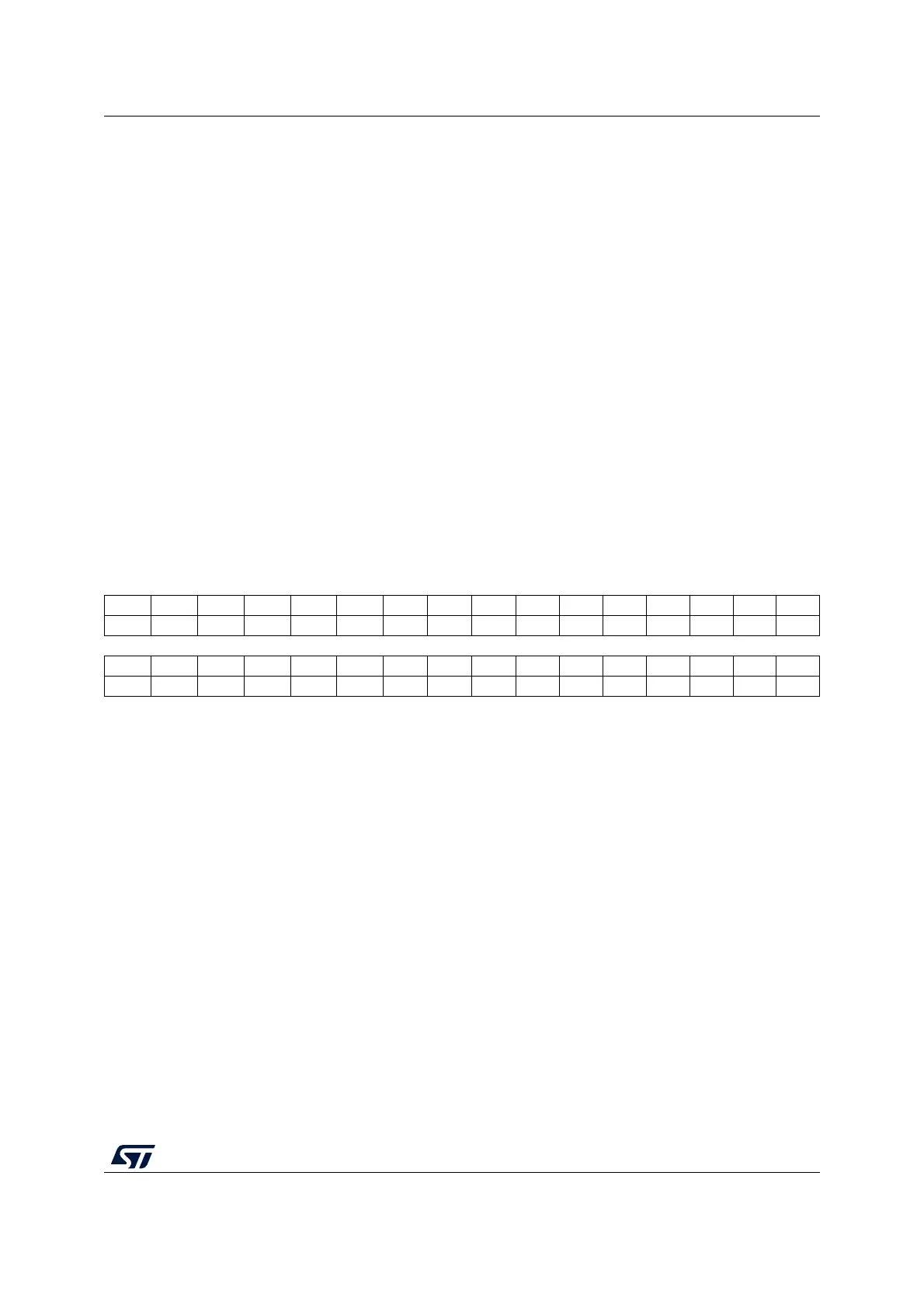

14.6.3 DMAMUX request line multiplexer interrupt channel clear flag register

(DMAMUX_CCFR)

Address offset: 0x084

Reset value: 0x0000 0000

This register must be written at bit level by a non-secure or secure write, according to the

secure mode of the considered DMAMUX request line multiplexer channel x, depending on

the secure control bit of the connected DMA controller channel y, and considering that the

DMAMUX x channel output is connected to the y channel of the DMA (refer to the

DMAMXUX mapping implementation section).

This register must be written at bit level by an unprivileged or privileged write, according to

the privileged mode of the considered DMAMUX request line multiplexer channel x,

Bit 9 EGE: Event generation enable

0: event generation disabled

1: event generation enabled

Bit 8 SOIE: Synchronization overrun interrupt enable

0: interrupt disabled

1: interrupt enabled

Bits 7:0 DMAREQ_ID[7:0]: DMA request identification

Selects the input DMA request. See the DMAMUX table about assignments of multiplexer

inputs to resources.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

Res. Res. SOF13 SOF12 SOF11 SOF10 SOF9 SOF8 SOF7 SOF6 SOF5 SOF4 SOF3 SOF2 SOF1 SOF0

rrrrrrrrrrrrrr

Bits 31:14 Reserved, must be kept at reset value.

Bits 13:0 SOF[13:0]: Synchronization overrun event flag

The flag is set when a synchronization event occurs on a DMA request line multiplexer

channel x, while the DMA request counter value is lower than NBREQ.

The flag is cleared by writing 1 to the corresponding CSOFx bit in DMAMUX_CFR

DMAMUX_CCFR register.

Loading...

Loading...