RM0453 Rev 1 1365/1461

RM0453 Debug support (DBG)

1448

There are four event channels in the CTM, thus enabling up to four, parallel, bidirectional

connections between trigger inputs and outputs on different CTIs. To connect input number

m on CTIx to output number n on CTIy, the input must be connected to an event channel p

using the CTI_INENRm register of CTIx. The same channel p must be connected to the

output using the CTI_OUTENRn register of CTIy.

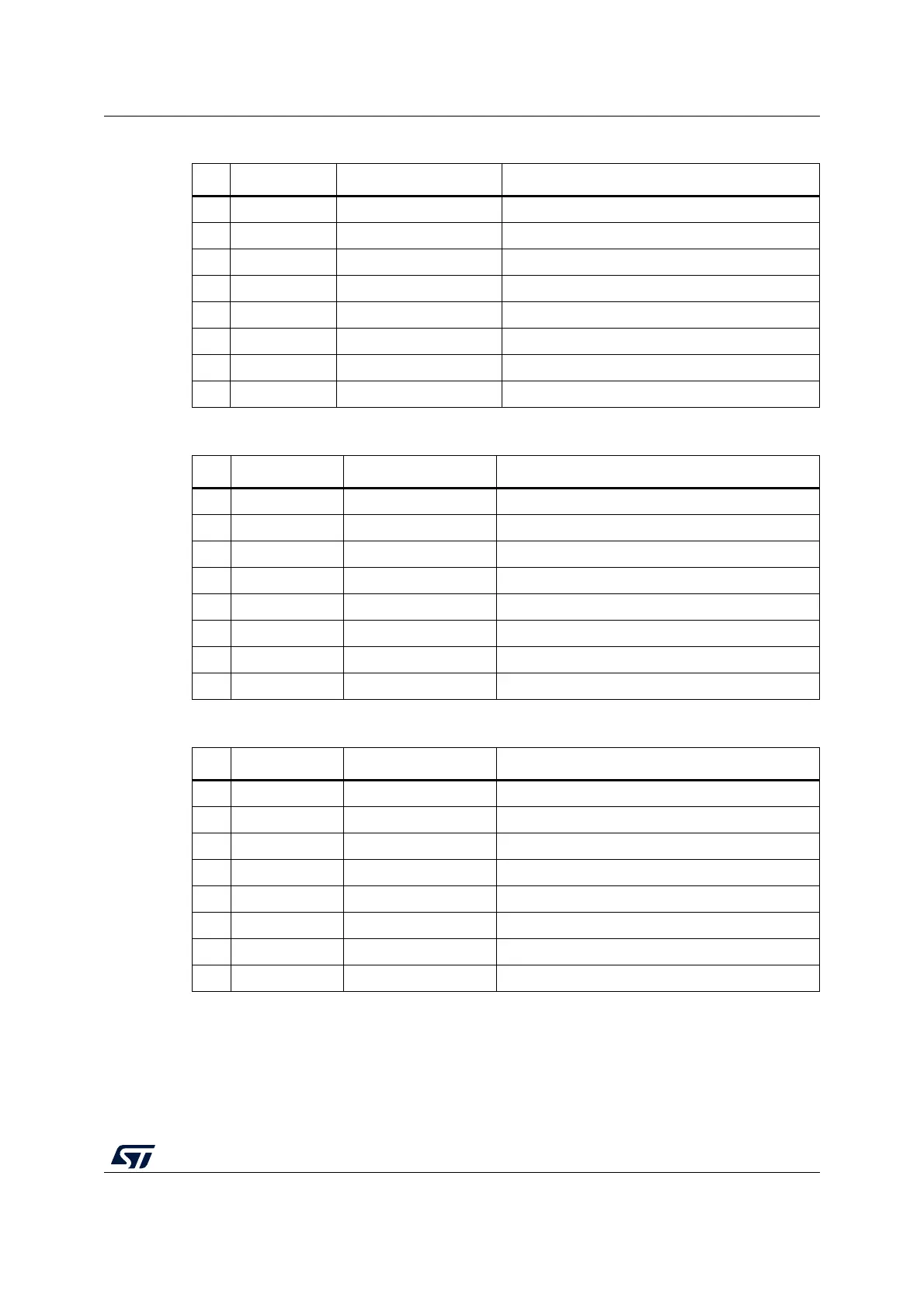

Table 273. CPU2 CTI outputs

No. Output signal Destination component Comments

0 EDBGRQ CPU2 CPU2 halt request - Puts CPU2 in debug mode.

1 - - Not used

2 - - Not used

3 - - Not used

4 - - Not used

5 - - Not used

6 - - Not used

7 DBGRESTART CPU2 CPU2 restart request - CPU2 exits debug mode.

Table 274. CPU1 CTI inputs

No. Source signal Source component Comments

0 HALTED CPU1 CPU1 halted - indicates CPU1 is in debug mode.

1 - - Not used

2 - - Not used

3 - - Not used

4 - - Not used

5 - - Not used

6 - - Not used

7 - - Not used

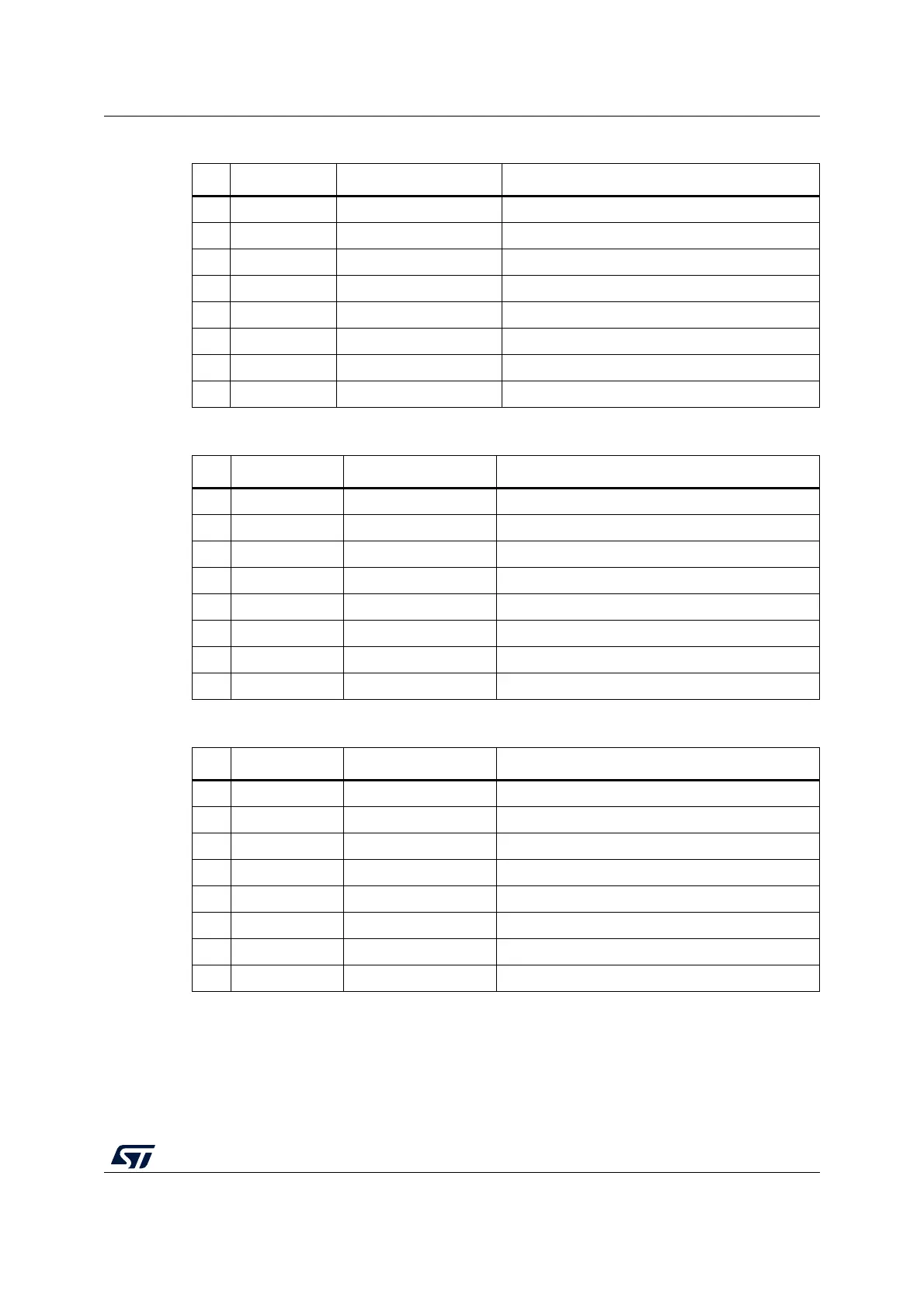

Table 275. CPU1 CTI outputs

No. Source signal Source component Comments

0 EDBGRQ CPU1 CPU1 halt request - Puts CPU1 in debug mode.

1 - - Not used

2 - - Not used

3 - - Not used

4 - - Not used

5 - - Not used

6 - - Not used

7 DBGRESTART CPU1 CPU1 restart request - CPU1 exits debug mode

Loading...

Loading...