Extended interrupts and event controller (EXTI) RM0453

512/1461 RM0453 Rev 1

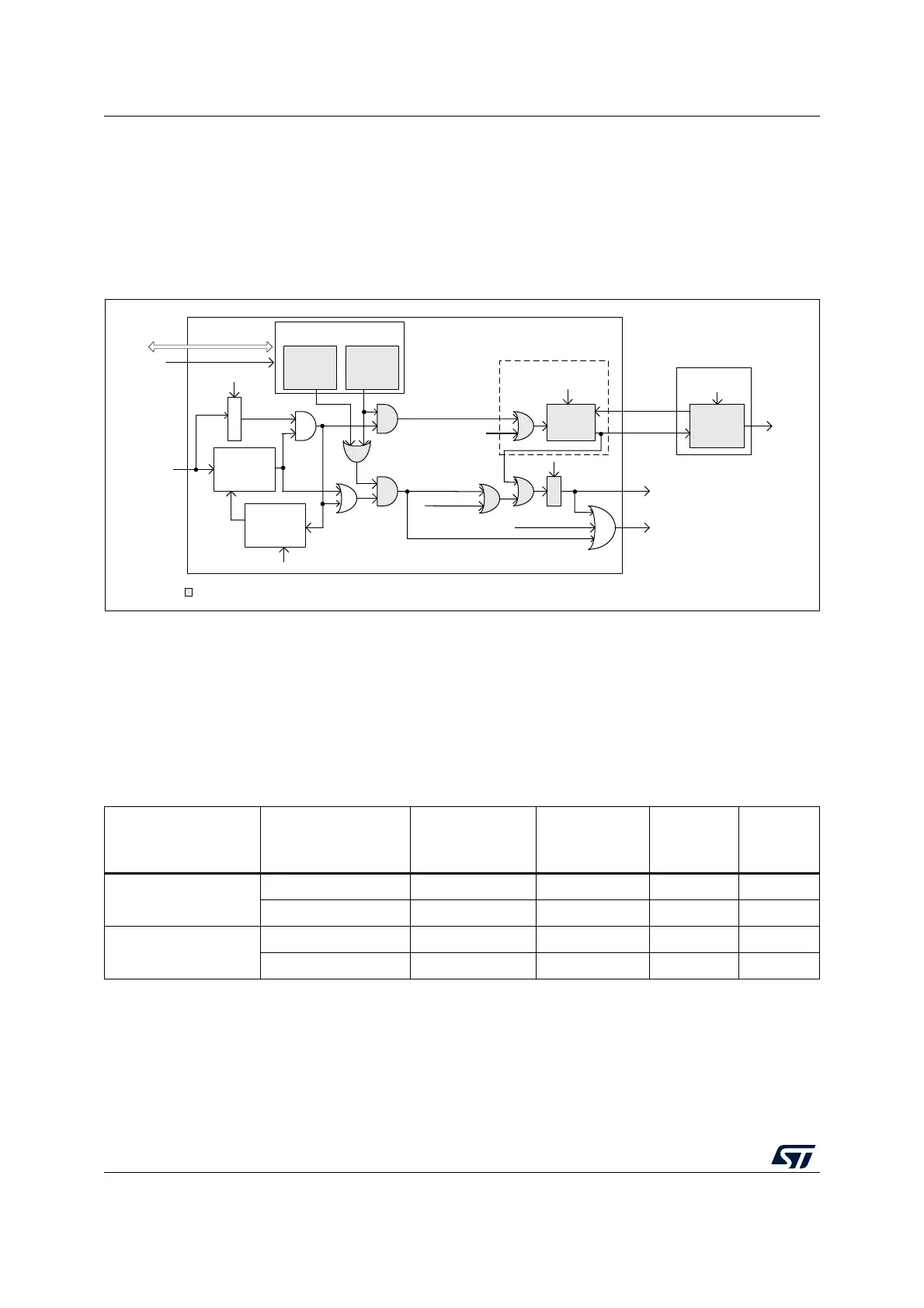

The direct events do not have an associated EXTI interrupt. The EXTI only wakes up the

system and CPU sub-system clocks and may generate a CPU wakeup event. The

peripheral synchronous interrupt associated with the direct wakeup event, wake up the

CPU. The EXTI direct event is able to generate a CPU event. This CPU event wakes up the

CPU.

The CPU event may occur before the associated peripheral interrupt flag is set.

Figure 56. Direct event trigger logic CPU wakeup

16.5 EXTI functional behavior

The direct event inputs are enabled in the respective peripheral generating the wakeup

event. The configurable events are enabled by enabling at least one of the trigger edges.

Once an event input is enabled, the generation of a CPU wakeup is conditioned by the CPU

interrupt mask and the CPU event mask.

For configurable event inputs, when the enabled edges occur on the event input, an event

request is generated. When the associated it_exti_per(y) interrupt is unmasked, the

corresponding pending bit in EXTI_PR is set, the CPU sub-system wakes up and the CPU

MSv60762V1

Peripheral interface

EVG

EXTI

Direct event

input(x)

Asynchronous

rising edge

detect circuit

Falling edge

detect pulse

generator

rst

Delay

hclk

CPUn

rising edge

detect pulse

generator

hclk

ck_fclk_cn

cn_event

cn_wakeup

sys_wakeupCPUn other wakeups

Other wakeups

CPUn event(x)

(1)

CPUn wakeup(x)

Wakeup(x)

Logic duplicated for each CPU

Synch

hclk

AHB

interface

CPUn

interrupt

mask register

cn_evt_exti

hclk

CPUn

other events(x,y)

Rising edge

detect

hclk

rst

cn_evt_rst

CPUn

event

mask register

1) Only for the input events supporting the CPUn rxrev generation cn_event.

Same circuit for configurable

and direct events

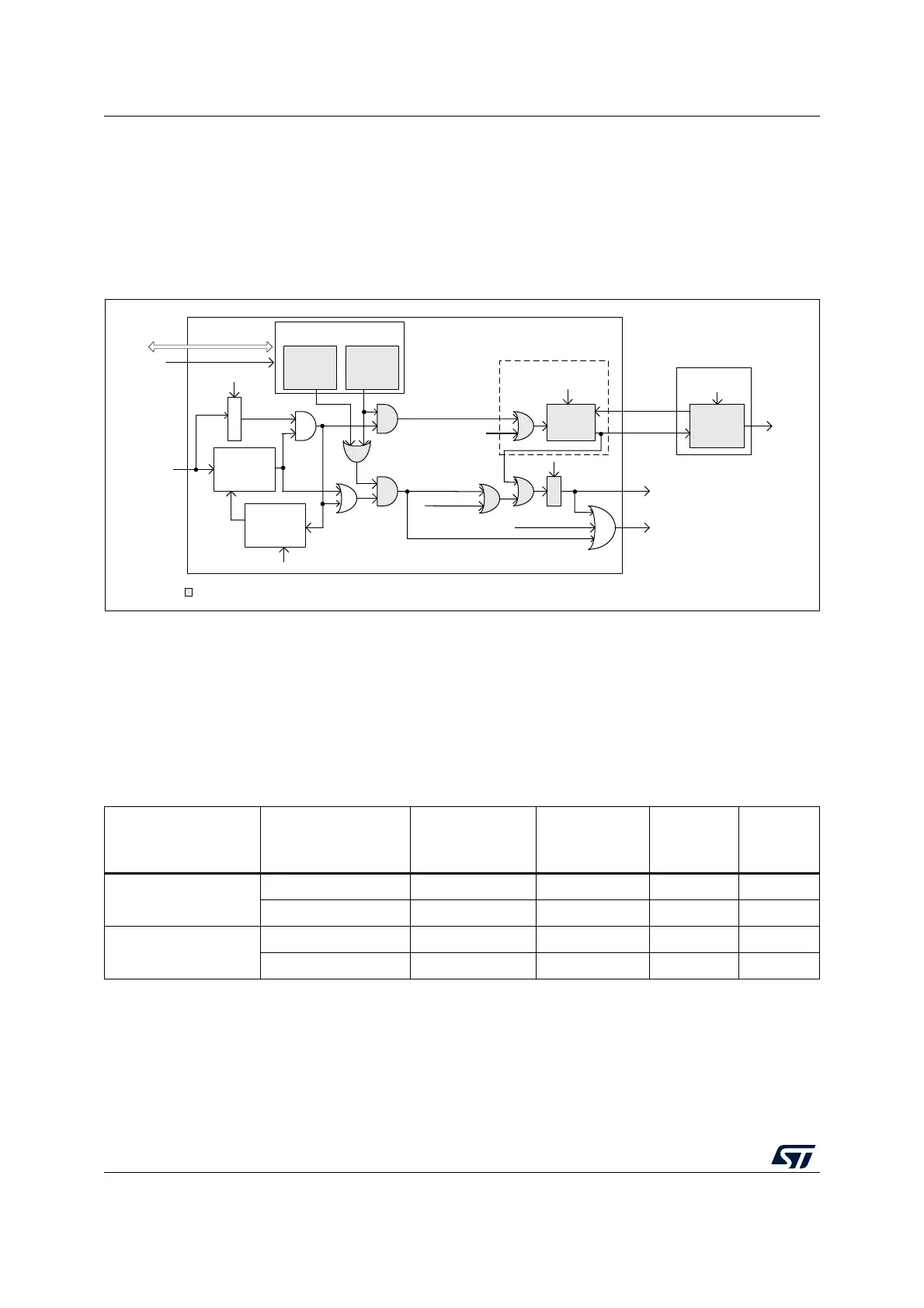

Table 95. Masking functionality

CPU interrupt enable

EXTI_CnIMRm.IMb

CPU event enable

EXTI_CnEMRm.EMb

Configurable

event inputs

EXTI_PRm.PIFb

it_exti_per(y)

(1)

CPUn event

CPUn

wakeup

0

0 No Masked Masked Masked

1 No Masked Yes Yes

1

0 Status latched Yes Masked Yes

(2)

1 Status latched Yes Yes Yes

1. The single it_exti_per(y) interrupt goes to both CPUs. If no interrupt is required for the CPUn, the it_exti_per(y) interrupt

must be masked in the CPUn NVIC.

2. Only if the CPU interrupt is enabled in EXTI_CnIMRm.IMb.

Loading...

Loading...