RM0453 Rev 1 1023/1461

RM0453 Real-time clock (RTC)

1057

32.6.6 RTC wakeup timer register (RTC_WUTR)

This register can be written only when WUTWF is set to 1 in RTC_ICSR.

Address offset: 0x14

Backup domain reset value: 0x0000 FFFF

System reset: not affected

32.6.7 RTC control register (RTC_CR)

This register is write protected. The write access procedure is described in RTC register

write protection on page 1007.

Address offset: 0x18

Backup domain reset value: 0x0000 0000

System reset: not affected

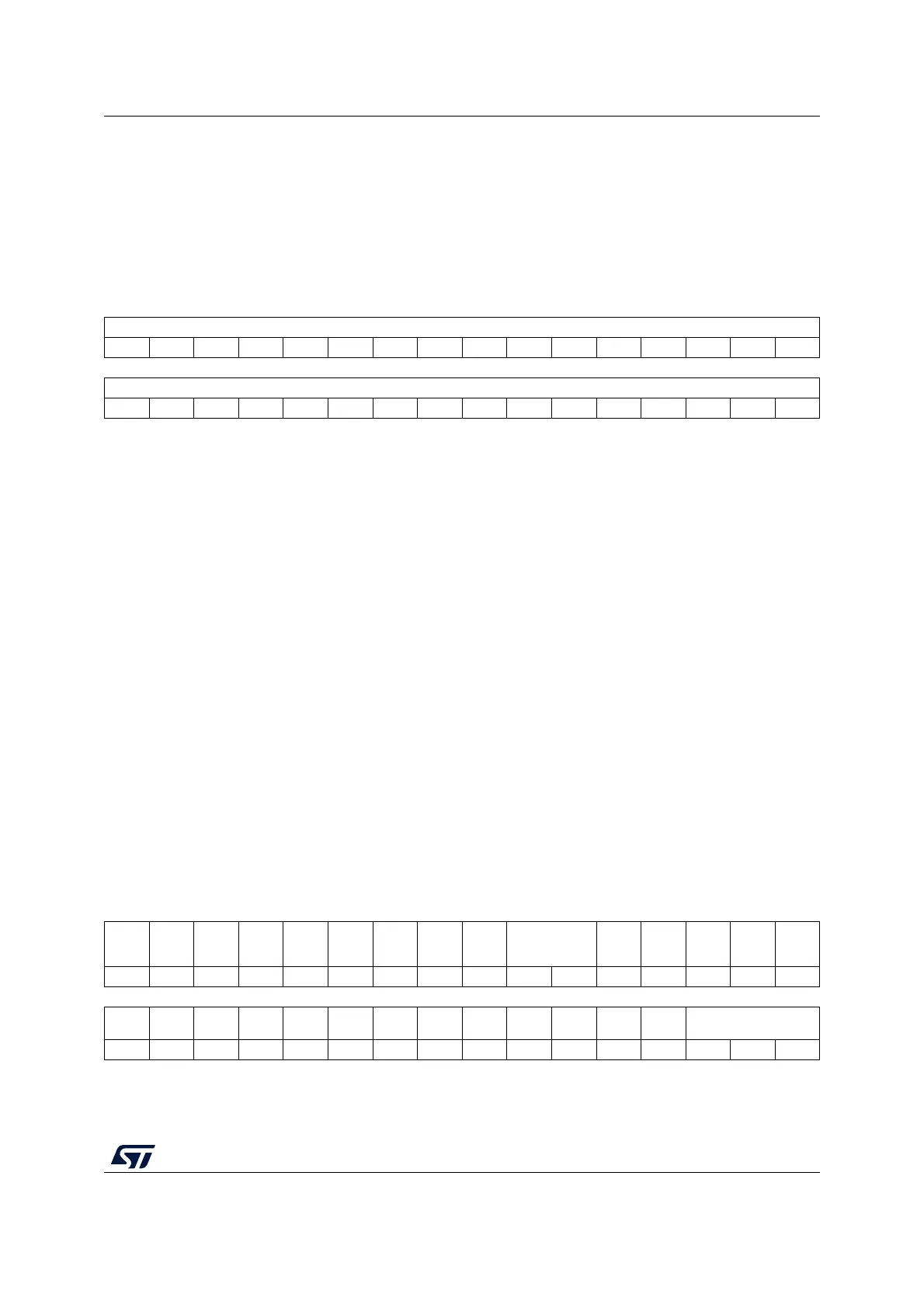

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

WUTOCLR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

WUT[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:16 WUTOCLR[15:0]: Wakeup auto-reload output clear value

When WUTOCLR[15:0] is different from 0x0000, WUTF is set by hardware when the auto-

reload down-counter reaches 0 and is cleared by hardware when the auto-reload

downcounter reaches WUTOCLR[15:0].

When WUTOCLR[15:0] = 0x0000, WUTF is set by hardware when the WUT down-counter

reaches 0 and is cleared by software.

Bits 15:0 WUT[15:0]: Wakeup auto-reload value bits

When the wakeup timer is enabled (WUTE set to 1), the WUTF flag is set every

(WUT[15:0] + 1) ck_wut cycles. The ck_wut period is selected through WUCKSEL[2:0] bits

of the RTC_CR register.

When WUCKSEL[2] = 1, the wakeup timer becomes 17-bits and WUCKSEL[1] effectively

becomes WUT[16] the most-significant bit to be reloaded into the timer.

The first assertion of WUTF occurs between WUT and (WUT + 2) ck_wut cycles after WUTE

is set. Setting WUT[15:0] to 0x0000 with WUCKSEL[2:0] = 011 (RTCCLK/2) is forbidden.

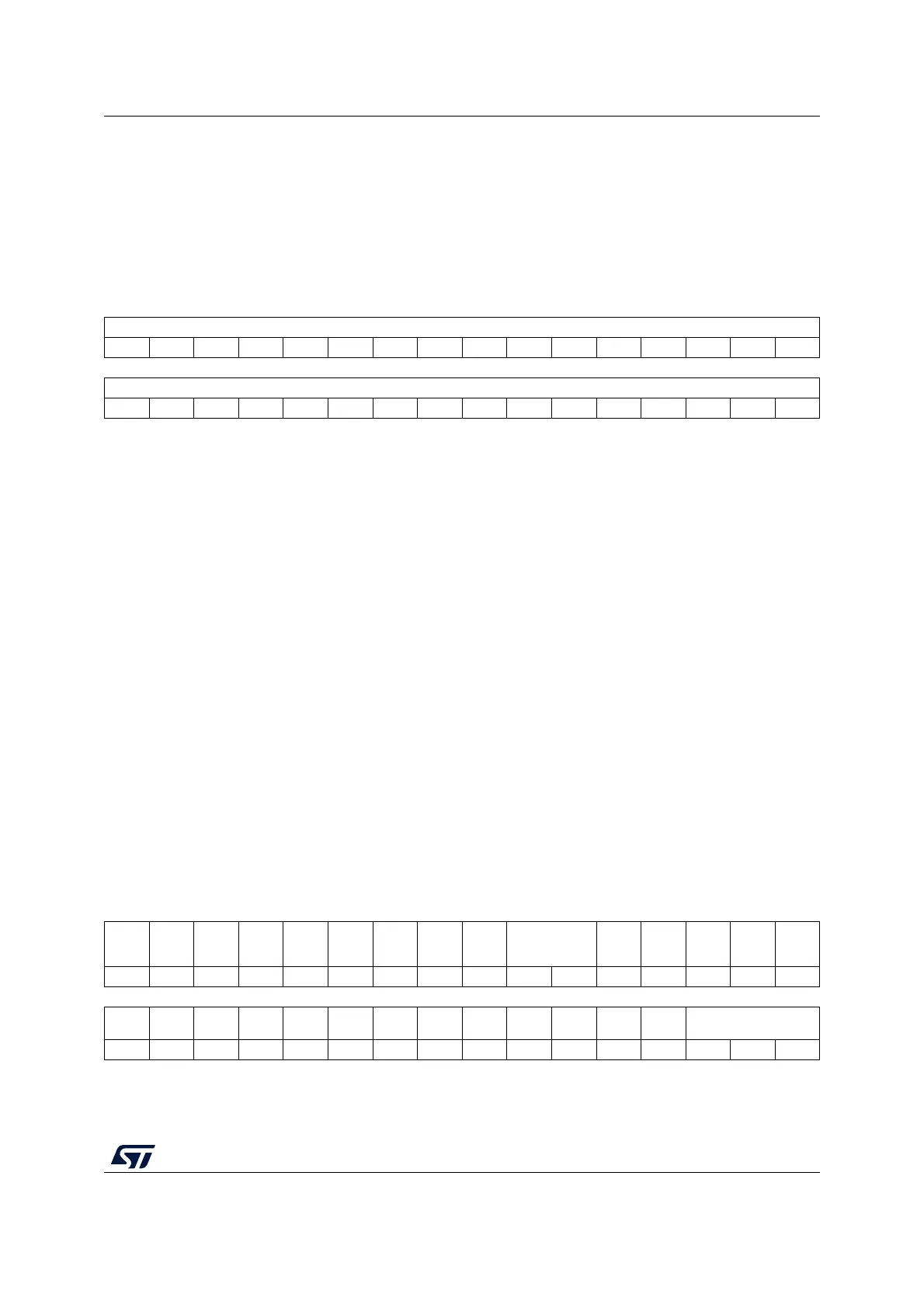

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

OUT2

EN

TAMP

ALRM_

TYPE

TAMP

ALRM_

PU

Res. Res.

TAMP

OE

TAMP

TS

ITSE COE OSEL[1:0] POL COSEL BKP SUB1H ADD1H

rw rw rw rw rw rw rw rw rw rw rw rw w w

1514131211109876543210

TSIE WUTIE

ALRB

IE

ALRA

IE

TSE WUTE ALRBE ALRAE

SSR

UIE

FMT

BYP

SHAD

REFCK

ON

TS

EDGE

WUCKSEL[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...