RM0453 Rev 1 965/1461

RM0453 Low-power timer (LPTIM)

981

28.4.15 Encoder mode

This mode allows handling signals from quadrature encoders used to detect angular

position of rotary elements. Encoder interface mode acts simply as an external clock with

direction selection. This means that the counter just counts continuously between 0 and the

auto-reload value programmed into the LPTIM_ARR register (0 up to ARR or ARR down to

0 depending on the direction). Therefore LPTIM_ARR must be configured before starting

the counter. From the two external input signals, Input1 and Input2, a clock signal is

generated to clock the LPTIM counter. The phase between those two signals determines

the counting direction.

The Encoder mode is only available when the LPTIM is clocked by an internal clock source.

The signals frequency on both Input1 and Input2 inputs must not exceed the LPTIM internal

clock frequency divided by 4. This is mandatory in order to guarantee a proper operation of

the LPTIM.

Direction change is signalized by the two Down and Up flags in the LPTIM_ISR register.

Also, an interrupt can be generated for both direction change events if enabled through the

DOWNIE bit.

To activate the Encoder mode the ENC bit has to be set to ‘1’. The LPTIM must first be

configured in Continuous mode.

When Encoder mode is active, the LPTIM counter is modified automatically following the

speed and the direction of the incremental encoder. Therefore, its content always

represents the encoder’s position. The count direction, signaled by the Up and Down flags,

correspond to the rotation direction of the encoder rotor.

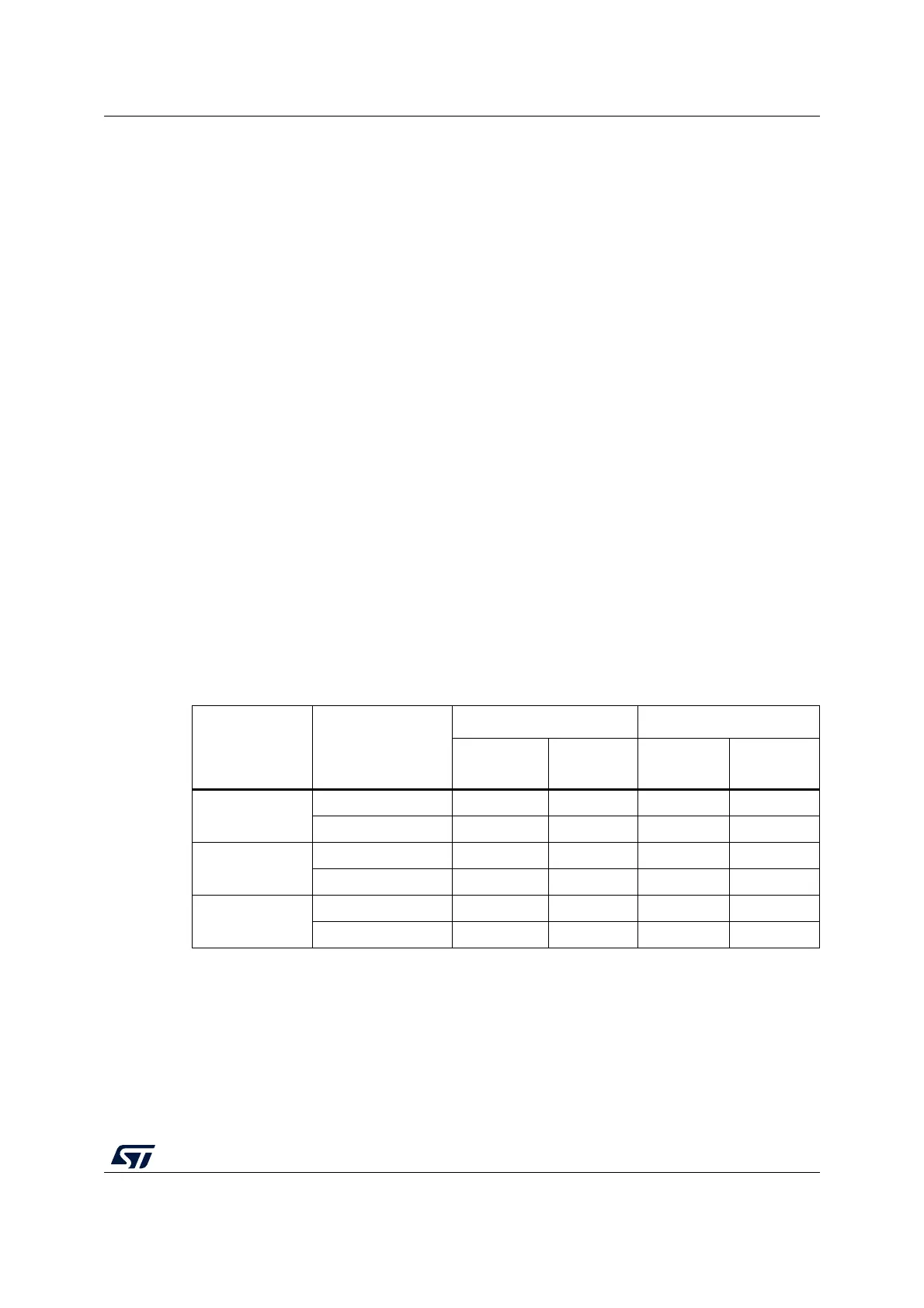

According to the edge sensitivity configured using the CKPOL[1:0] bits, different counting

scenarios are possible. The following table summarizes the possible combinations,

assuming that Input1 and Input2 do not switch at the same time.

The following figure shows a counting sequence for Encoder mode where both-edge

sensitivity is configured.

Caution: In this mode the LPTIM must be clocked by an internal clock source, so the CKSEL bit must

be maintained to its reset value which is equal to ‘0’. Also, the prescaler division ratio must

be equal to its reset value which is 1 (PRESC[2:0] bits must be ‘000’).

Table 200. Encoder counting scenarios

Active edge

Level on opposite

signal (Input1 for

Input2, Input2 for

Input1)

Input1 signal Input2 signal

Rising Falling Rising Falling

Rising Edge

High Down No count Up No count

Low Up No count Down No count

Falling Edge

High No count Up No count Down

Low No count Down No count Up

Both Edges

High Down Up Up Down

Low Up Down Down Up

Loading...

Loading...