RM0453 Rev 1 305/1461

RM0453 Reset and clock control (RCC)

364

7.4.4 RCC PLL configuration register (RCC_PLLCFGR)

Address offset: 0x00C

Reset value: 0x2204 0100

Access: no wait state, word, half-word and byte access

This register is used to configure the main PLL clock outputs according to the formulas:

• f(VCO clock) = f(PLL clock input) × (PLLN / PLLM)

• f(PLL_P) = f(VCO clock) / PLLP

• f(PLL_Q) = f(VCO clock) / PLLQ

• f(PLL_R) = f(VCO clock) / PLLR

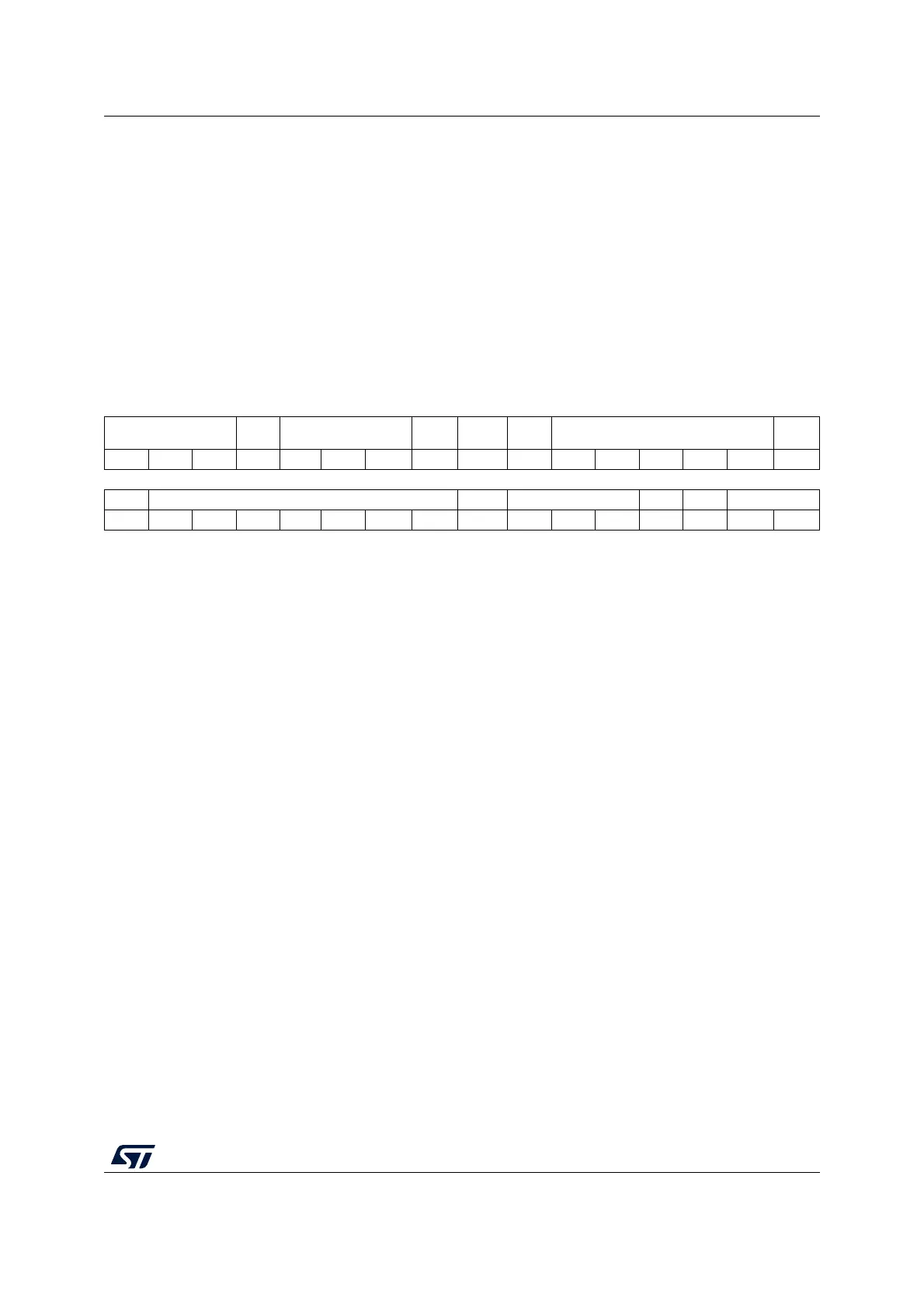

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

PLLR[2:0]

PLL

REN

PLLQ[2:0]

PLL

QEN

Res. Res. PLLP[4:0]

PLL

PEN

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

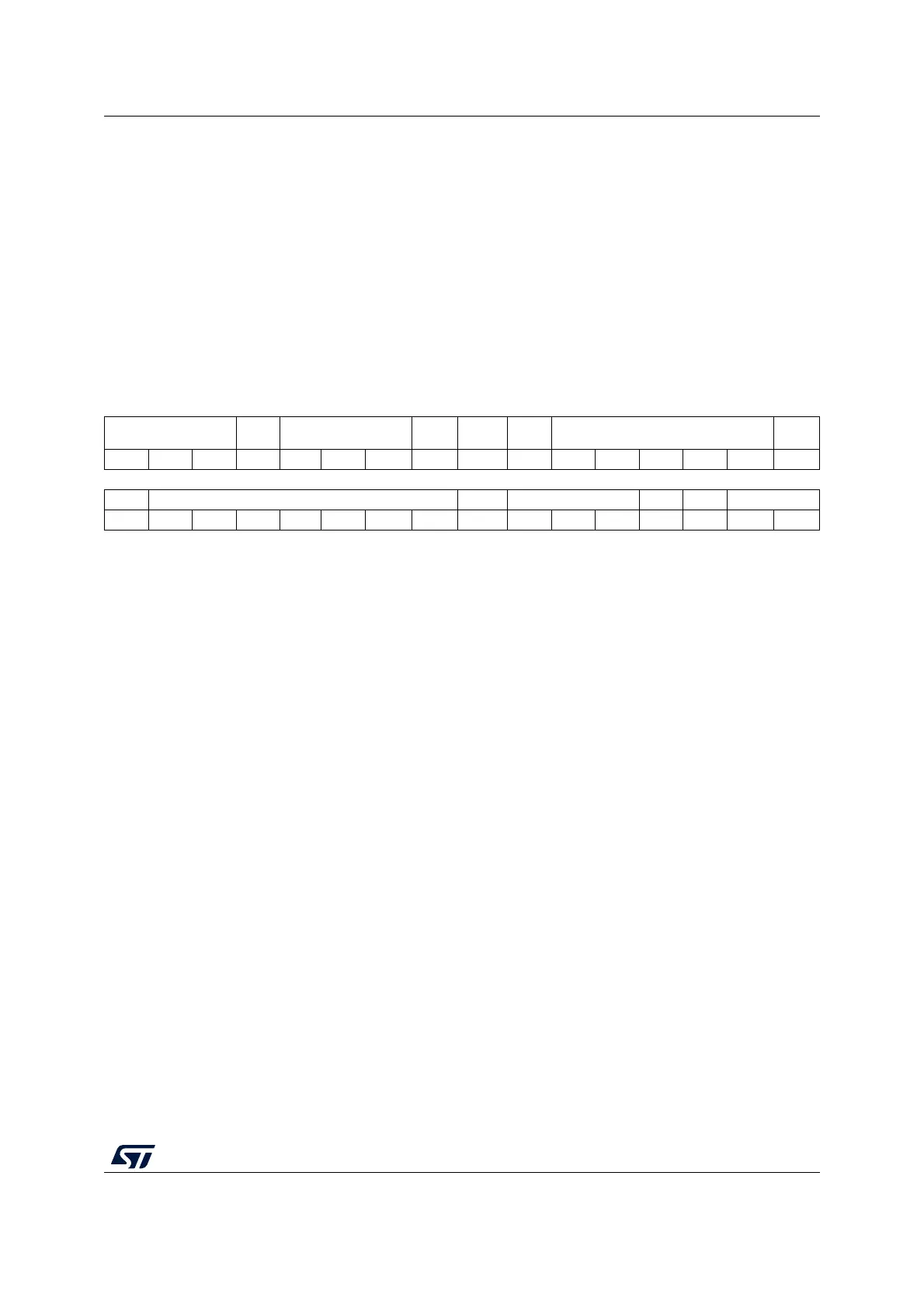

1514131211109 8 7 654321 0

Res. PLLN[6:0] Res. PLLM[2:0] Res. Res. PLLSRC[1:0]

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:29 PLLR[2:0]: Main PLL division factor for PLLRCLK

These bits are set and cleared by software to control the frequency of the main PLL output

clock PLLRCLK. This output can be selected as system clock. These bits can be written only

if PLL is disabled.

PLLRCLK output clock frequency = VCO frequency / PLLR with PLLR = 2, 3, 4,... or 8 [VCO

frequency / (N + 1)]

000: reserved

001: PLLR = 2

010: PLLR = 3

011: PLLR = 4

100: PLLR = 5

101: PLLR = 6

110: PLLR = 7

111: PLLR = 8

Note: The software must set these bits correctly not to exceed 48 MHz on this domain in

range 1.

Bit 28 PLLREN: Main PLL PLLRCLK output enable

This bit is set and reset by software to enable the PLLRCLK output of the main PLL. It

cannot be written when PLLRCLK output of the PLL is used as system clock. In order to

save power, when the PLLRCLK output of the PLL is not used, the value of PLLREN must

be 0.

0: PLLRCLK output disabled

1: PLLRCLK output enabled

Loading...

Loading...