RM0453 Rev 1 691/1461

RM0453 AES hardware accelerator (AES)

698

23.7.4 AES data output register (AES_DOUTR)

Address offset: 0x0C

Reset value: 0x0000 0000

Only 32-bit read access type is supported.

Bits 31:0 DIN[31:0]: Input data word

A four-fold sequential write to this bitfield during the input phase results in writing a complete 128-bit

block of input data to the AES peripheral. From the first to the fourth write, the corresponding data

weights are [127:96], [95:64], [63:32], and [31:0]. Upon each write, the data from the 32-bit input

buffer are handled by the data swap block according to the DATATYPE[1:0] bitfield, then written into

the AES core 128-bit input buffer.

The data signification of the input data block depends on the AES operating mode:

- Mode 1 (encryption): plaintext

- Mode 2 (key derivation): the bitfield is not used (AES_KEYRx registers used for input)

- Mode 3 (decryption): ciphertext

The data swap operation is described in Section 23.4.13: AES data registers and data swapping on

page 681.

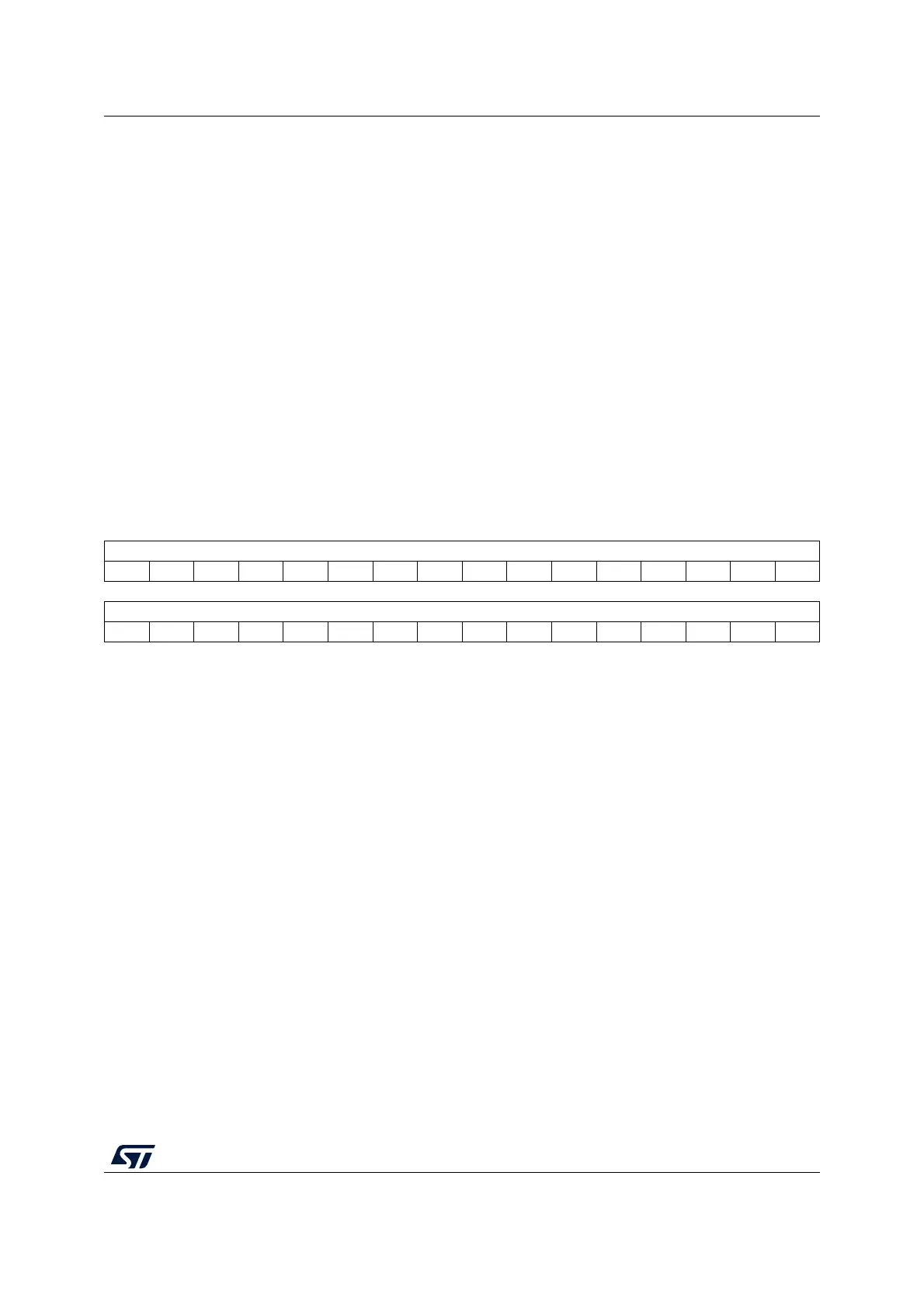

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DOUT[31:16]

rrrrrrrrrrrrrrrr

1514131211109876543210

DOUT[15:0]

rrrrrrrrrrrrrrrr

Bits 31:0 DOUT[31:0]: Output data word

This read-only bitfield fetches a 32-bit output buffer. A four-fold sequential read of this bitfield, upon

the computation completion (CCF set), virtually reads a complete 128-bit block of output data from

the AES peripheral. Before reaching the output buffer, the data produced by the AES core are

handled by the data swap block according to the DATATYPE[1:0] bitfield.

Data weights from the first to the fourth read operation are: [127:96], [95:64], [63:32], and [31:0].

The data signification of the output data block depends on the AES operating mode:

- Mode 1 (encryption): ciphertext

- Mode 2 (key derivation): the bitfield is not used

- Mode 3 (decryption): plaintext

The data swap operation is described in Section 23.4.13: AES data registers and data swapping on

page 681.

Loading...

Loading...