Direct memory access controller (DMA) RM0453

466/1461 RM0453 Rev 1

13.5 DMA interrupts

An interrupt can be generated on a half transfer, transfer complete or transfer error for each

DMA channel x (whatever the channel is secure or non-secure). Separate interrupt enable

bits are available for flexibility.

13.6 DMA registers

Refer to Section 1.2 for a list of abbreviations used in register descriptions.

The DMA registers have to be accessed by words (32-bit).

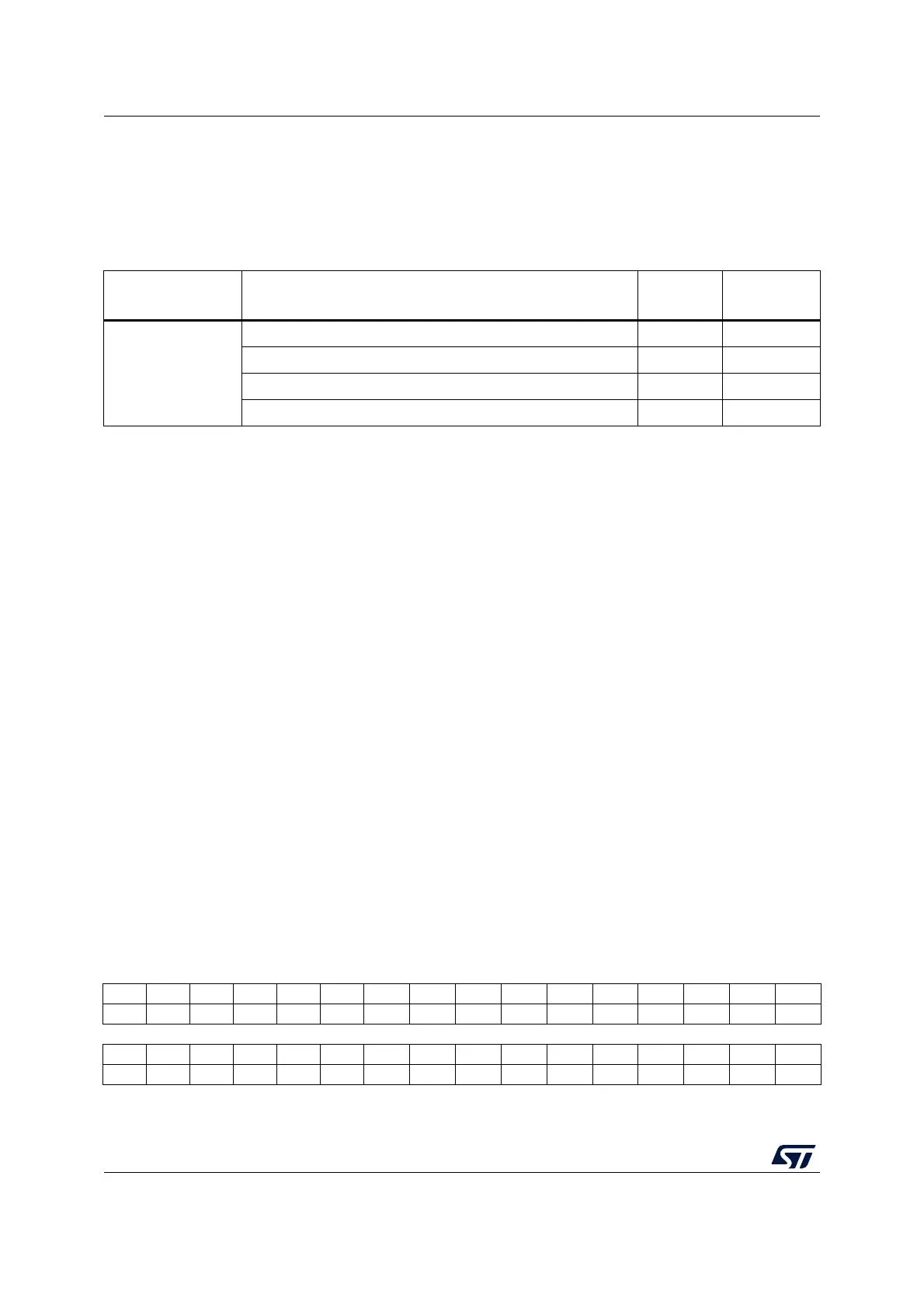

13.6.1 DMA interrupt status register (DMA_ISR)

Address offset: 0x00

Reset value: 0x0000 0000

This register may mix secure and non secure information, depending on the secure mode of

each channel (SECM bit of the DMA_CCRx register). A secure software can read the full

interrupt status. A non-secure software is restricted to read the status of non-secure

channel(s), other secure bit fields returning zero.

This register may mix privileged and unprivileged information, depending on the privileged

mode of each channel (PRIV bit of the DMA_CCRx register). A privileged software can read

the full interrupt status. An unprivileged software is restricted to read the status of

unprivileged channel(s), other privileged bit fields returning zero.

Every status / flag bit is set by hardware, independently of the privileged and the secure

mode of the channel.

Every status bit is cleared by hardware when the software sets the corresponding clear bit

or the corresponding global clear bit CGIFx, in the DMA_IFCR register, provided that, if the

channel x is in privileged mode and/or in secure mode, then the software access to

DMA_IFCR is also privileged and/or secure.

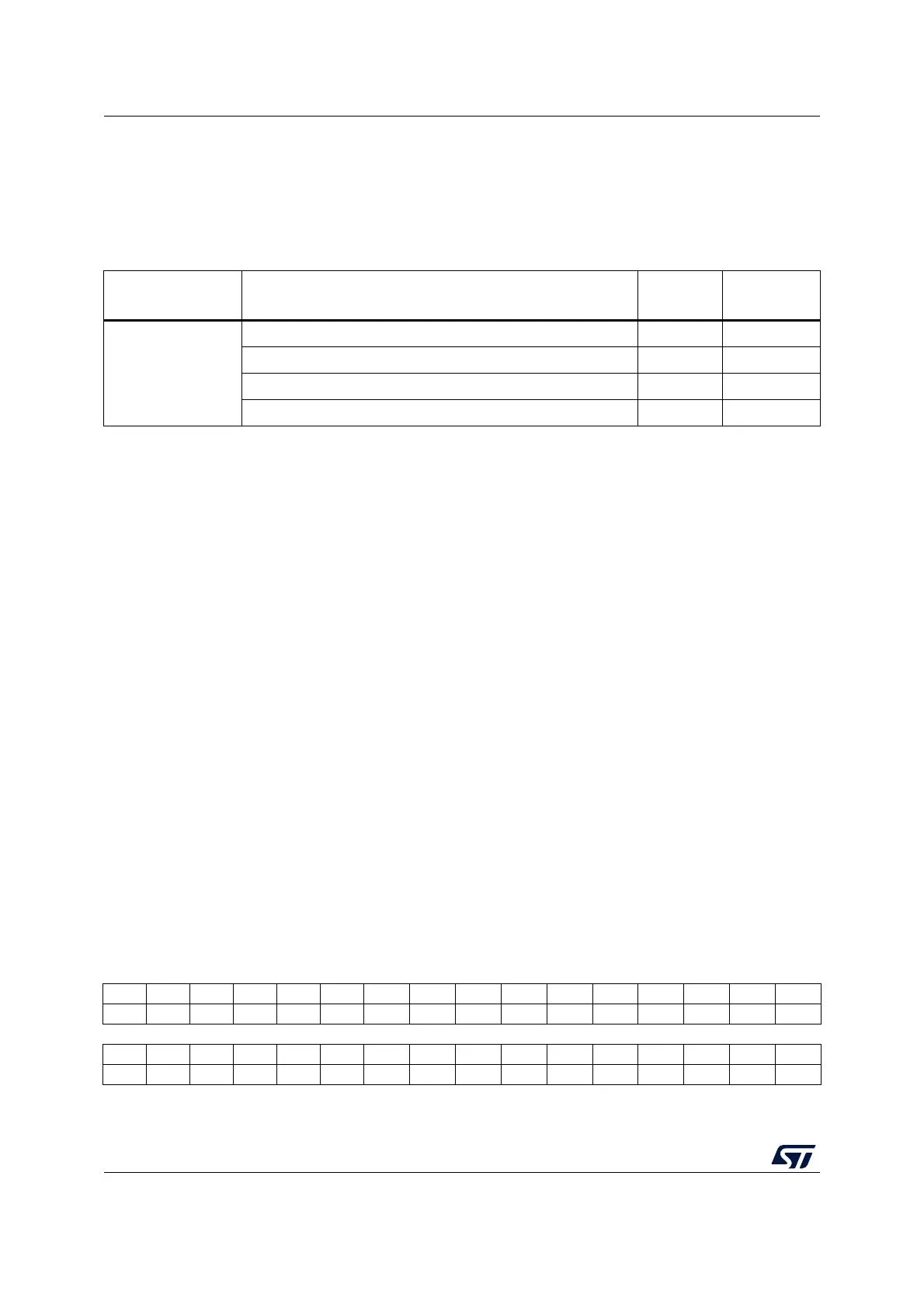

Table 80. DMA interrupt requests

Interrupt request Interrupt event Event flag

Interrupt

enable bit

Channel x interrupt

Half transfer on channel x HTIFx HTIEx

Transfer complete on channel x TCIFx TCIEx

Transfer error on channel x TEIFx TEIEx

Half transfer or transfer complete or transfer error on channel x GIFx -

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. TEIF7 HTIF7 TCIF7 GIF7 TEIF6 HTIF6 TCIF6 GIF6 TEIF5 HTIF5 TCIF5 GIF5

rrrrrrrrrrrr

1514131211109876543210

TEIF4 HTIF4 TCIF4 GIF4 TEIF3 HTIF3 TCIF3 GIF3 TEIF2 HTIF2 TCIF2 GIF2 TEIF1 HTIF1 TCIF1 GIF1

rrrrrr r r r r rrrrrr

Loading...

Loading...