RM0453 Rev 1 521/1461

RM0453 Extended interrupts and event controller (EXTI)

524

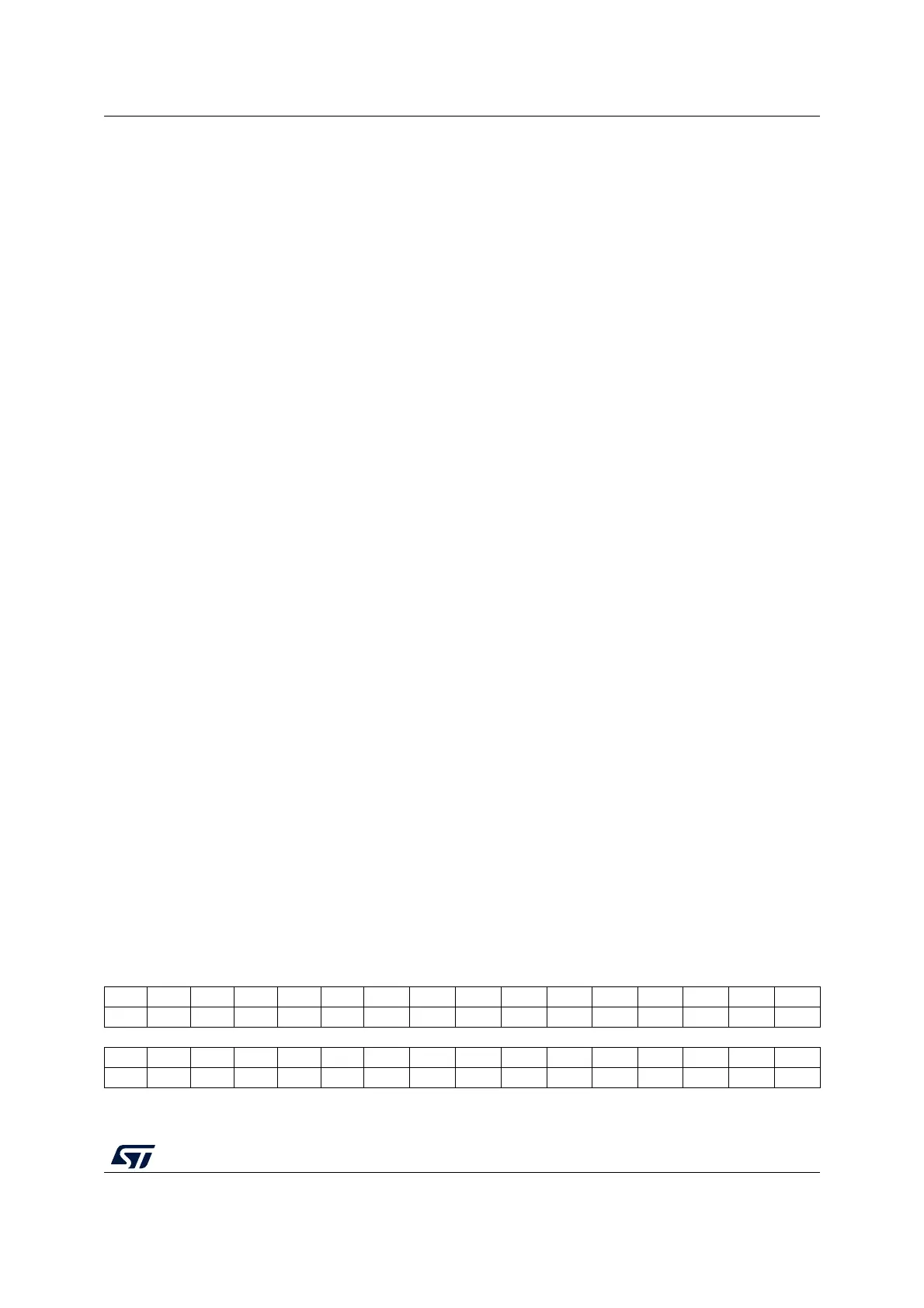

16.6.11 EXTI interrupt mask register (EXTI_CnIMR2)

Address offset: Block 1: 0x090

Address offset: Block 2: 0x0D0

Reset value: 0x0000 0000

Bits 31:23 Reserved, must be kept at reset value.

Bit 22 EM22: wakeup with event generation mask on event input 22

0: Event request from line 22 is masked.

1: Event request from line 22 is unmasked.

Bit 21 EM21: wakeup with event generation mask on event input 21

Bit 20 EM20: wakeup with event generation mask on event input 20

Bit 19 EM19: wakeup with event generation mask on event input 19

Bit 18 EM18: wakeup with event generation mask on event input 18

Bit 17 EM17: wakeup with event generation mask on event input 17

Bit 16 Reserved, must be kept at reset value.

Bit 15 EM15: wakeup with event generation mask on event input 15

Bit 14 EM14: wakeup with event generation mask on event input 14

Bit 13 EM13: wakeup with event generation mask on event input 13

Bit 12 EM12: wakeup with event generation mask on event input 12

Bit 11 EM11: wakeup with event generation mask on event input 11

Bit 10 EM10: wakeup with event generation mask on event input 10

Bit 9 EM9: wakeup with event generation mask on event input 19

Bit 8 EM8: wakeup with event generation mask on event input 8

Bit 7 EM7: wakeup with event generation mask on event input 7

Bit 6 EM6: wakeup with event generation mask on event input 6

Bit 5 EM5: wakeup with event generation mask on event input 5

Bit 4 EM4: wakeup with event generation mask on event input 4

Bit 3 EM3: wakeup with event generation mask on event input 3

Bit 2 EM2: wakeup with event generation mask on event input 2

Bit 1 EM1: wakeup with event generation mask on event input 1

Bit 0 EM0: wakeup with event generation mask on event input 0

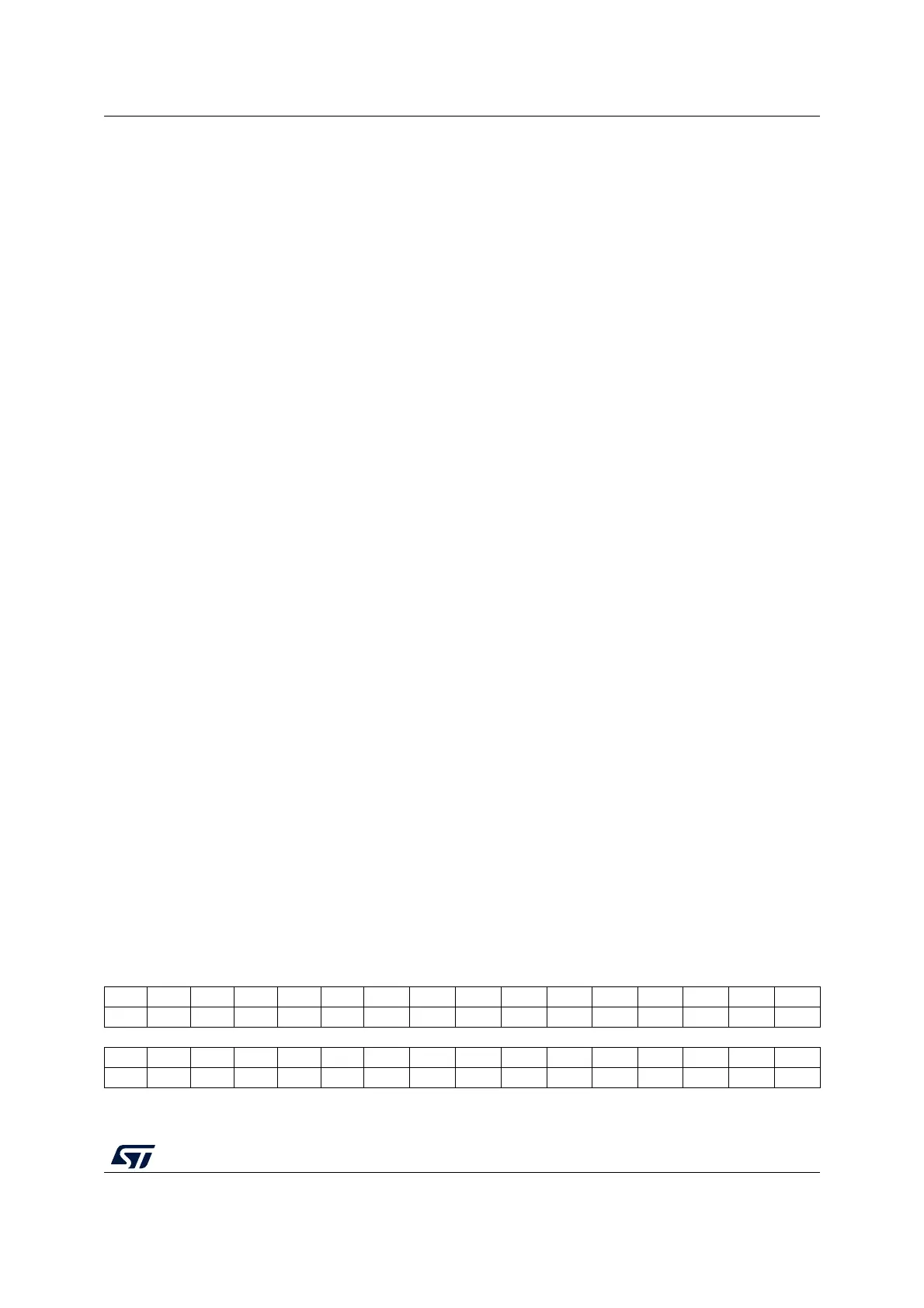

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. IM46 IM45 IM44 IM43 IM42 IM41 IM40 IM39 IM38 IM37 IM36 Res. IM34 Res. Res.

rw rw rw rw rw rw rw rw rw rw rw rw

Loading...

Loading...