RM0453 Rev 1 99/1461

RM0453 Embedded Flash memory (FLASH)

153

boot from. It prevents the system to boot from the Flash main memory area when, for

example, no user code is programmed.

The Flash main memory empty check status can be read from the EMPTY bit in the

FLASH_ACR register. Software can modify the Flash main memory empty status by writing

to the EMPTY bit.

4.3.3 Error code correction (ECC)

Data in Flash memory words are 72-bit wide: eight bits are added per each double-word

(64 bits).

The ECC mechanism supports the following modes:

• one error detection and correction

• two errors detection

When one error is detected and corrected, the flag ECCC (ECC correction) is set in

FLASH_ECCR. If ECCCIE is set, an interrupt is generated.

When two errors are detected, the flag ECCD (ECC detection) is set in FLASH_ECCR. In

this case, an NMI is generated.

When an ECC error is detected, the address of the failing double-word is saved in

ADDR_ECC[16:0] in FLASH_ECCR. ADDR_ECC[2:0] bits are always cleared. The bus-ID

of the CPU accessing the address is saved in CPUID[2:0].

While ECCC or ECCD is set, FLASH_ECCR is not updated if a new ECC error occurs.

FLASH_ECCR is updated only when ECC flags are cleared.

Note: For a virgin data (0xFF FFFF FFFF FFFF FFFF), one error is detected and corrected, but

the two errors detection mode is not supported.

When an ECC error is reported, a new read at the failing address may not generate an ECC

error if the data is still present in the current buffer, even if ECCC and ECCD are cleared. If

this is not the desired behavior, the user must reset the cache.

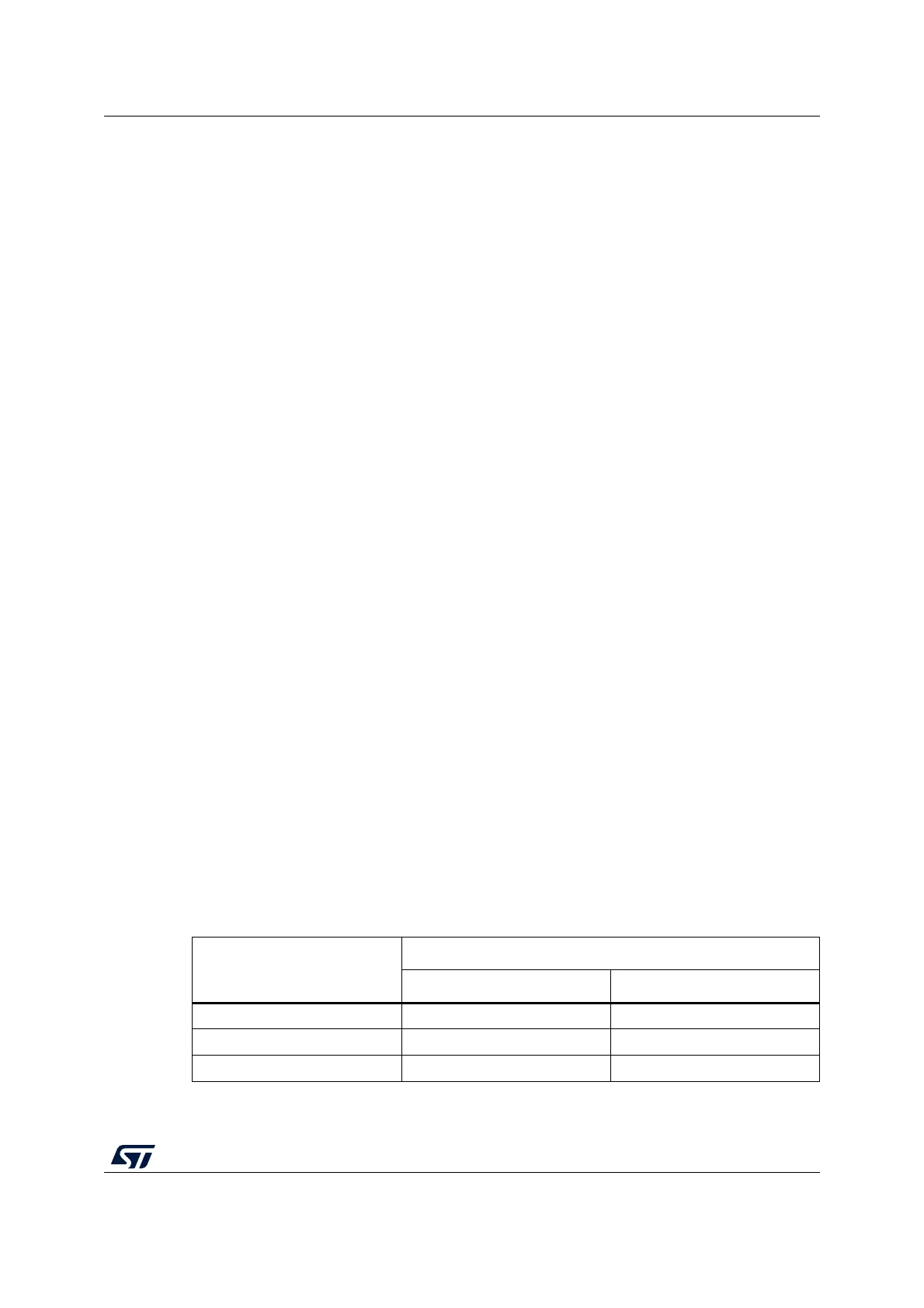

4.3.4 Read access latency

To correctly read data from the Flash memory, the number of wait states (LATENCY[2:0])

must be correctly programmed in FLASH_ACR according to the frequency of the Flash

memory clock (HCLK3) and the internal voltage range of the device (V

CORE

). Refer to

Section 6.1.4: Dynamic voltage scaling management.

The table below shows the correspondence between wait states and frequency of the Flash

memory clock.

Table 12. Number of wait states according to Flash clock (HCLK3) frequency

Wait states (WS)

(access)

HCLK3 (MHz)

V

CORE

range 1 V

CORE

range 2

0 WS (1 HCLK cycle) ≤ 18 ≤ 6

1 WS (2 HCLK cycles) ≤ 36 ≤ 12

2 WS (3 HCLK cycles) ≤ 48 ≤ 16

Loading...

Loading...