Inter-processor communication controller (IPCC) RM0453

384/1461 RM0453 Rev 1

Once the processor A retrieved the response from the memory, it does not change the

channel status flags. The memory location access is kept by processor A for the next

communication data.

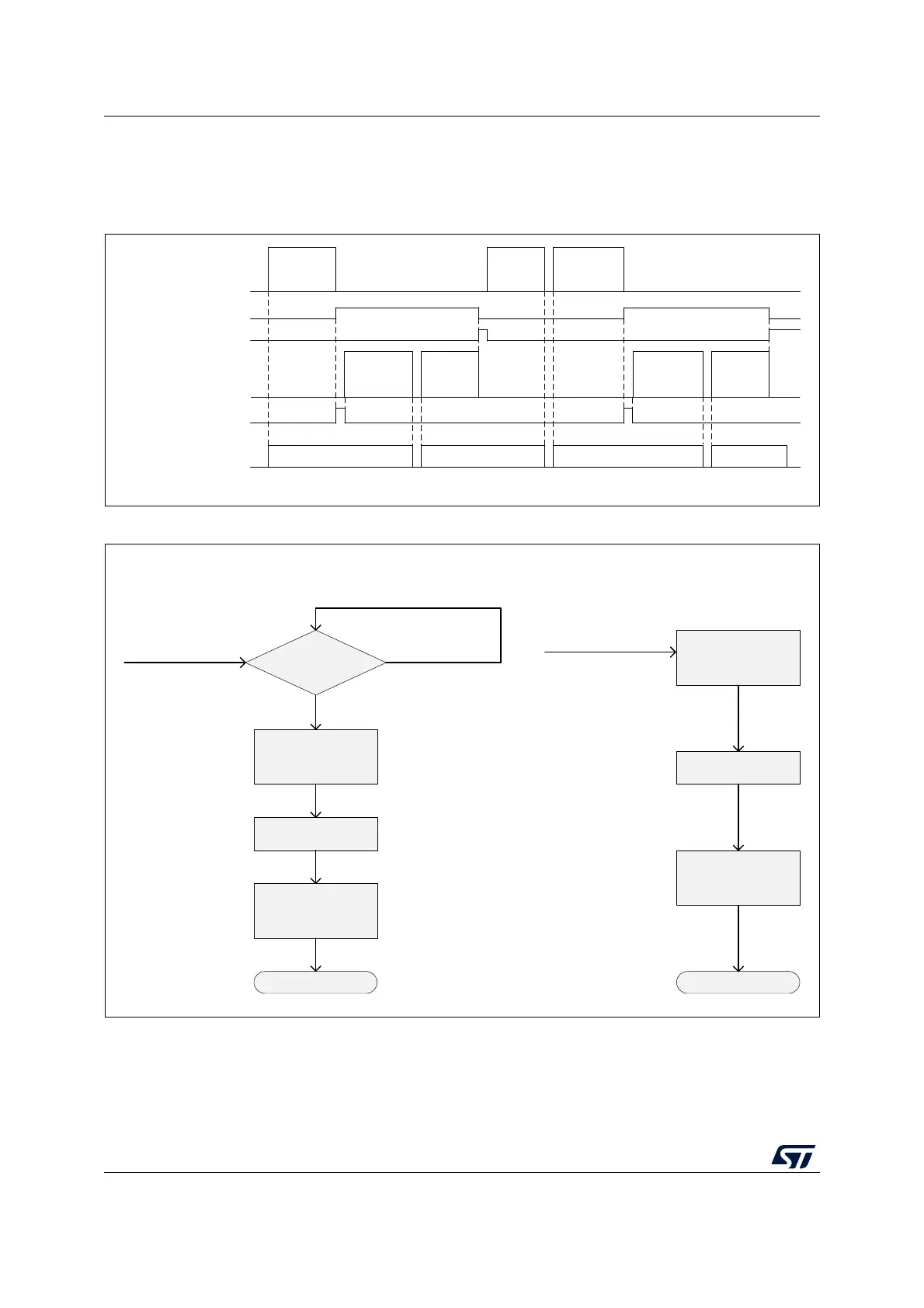

Figure 40. IPCC Half-duplex channel mode transfer timing

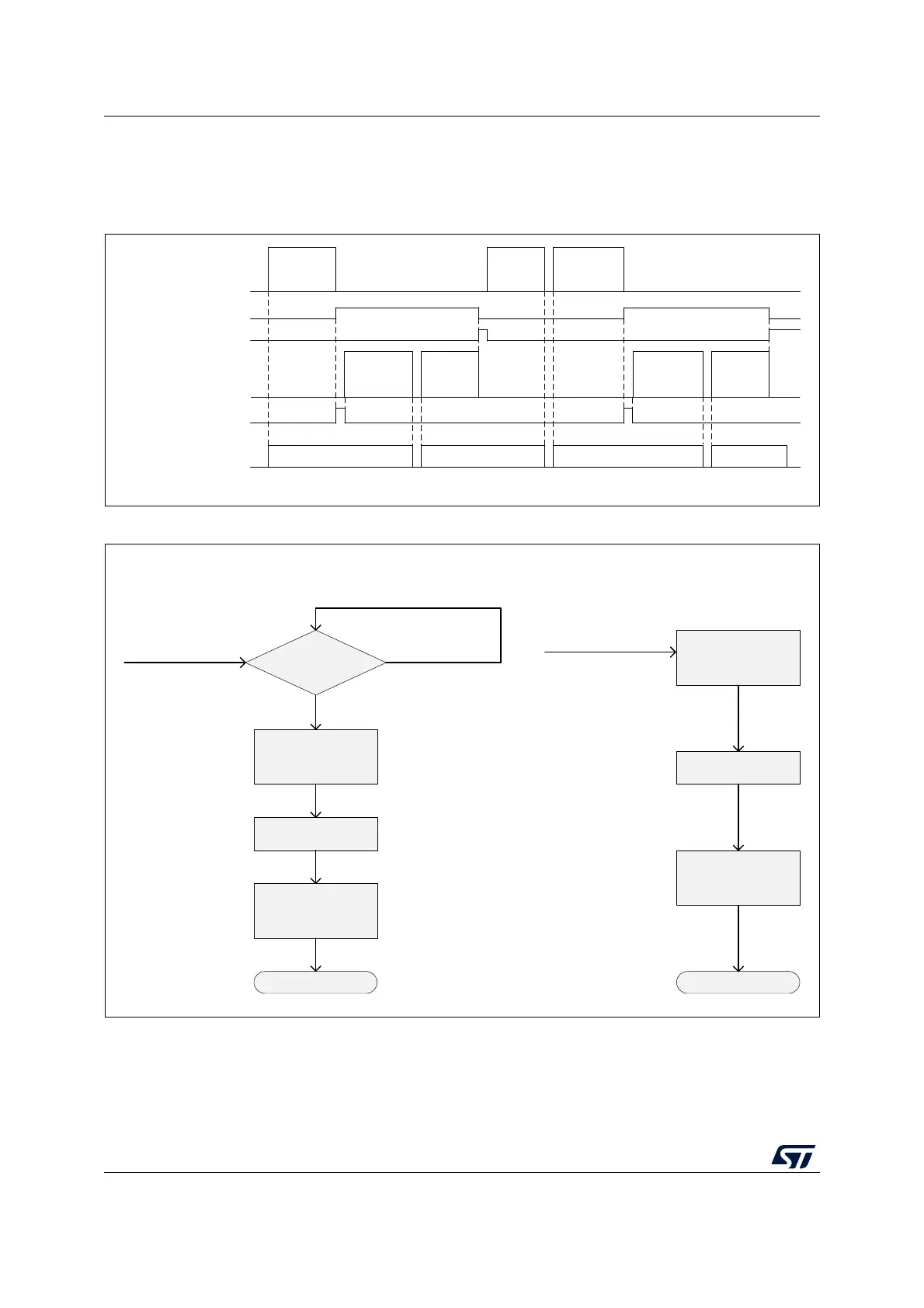

Figure 41. IPCC Half-duplex - Send procedure state diagram

MS42435V1

Processor A

Processor B

CHnF

TX free interrupt

RX occupied interrupt

Memory occupation

Write

Communication

data

Communication data

Read

Communication

data

Write

Response

Write

Communication

data

Read

Response

Response

Read

Communication

data

Write

Response

Communication data Response

MS42433V1

UNMASK

Channel N

free interrupt

Write

Communication

data to Memory

Set Channel N

occupied

End

Response pending = 1

Send

Communication data

Wait for

Response read

Response pending = 0

Communication processor A

Write CHnFM = 0

Write CHnS (set CHnF = 1)

Complete communication posted Write response pending = 1

Response processor B

Write Response

to Memory

Complete communication posted

Write response pending = 0

Clear Channel N free

UNMASK

Channel N

occupied interrupt

End

Response pending = 1

Write CHnC (set CHnF = 0)

Write CHnOM = 0

Loading...

Loading...