Reset and clock control (RCC) RM0453

340/1461 RM0453 Rev 1

7.4.32 RCC extended clock recovery register (RCC_EXTCFGR)

Address offset: 0x108

Reset value: 0x0003 0000

Access: no wait state, word, half-word and byte access

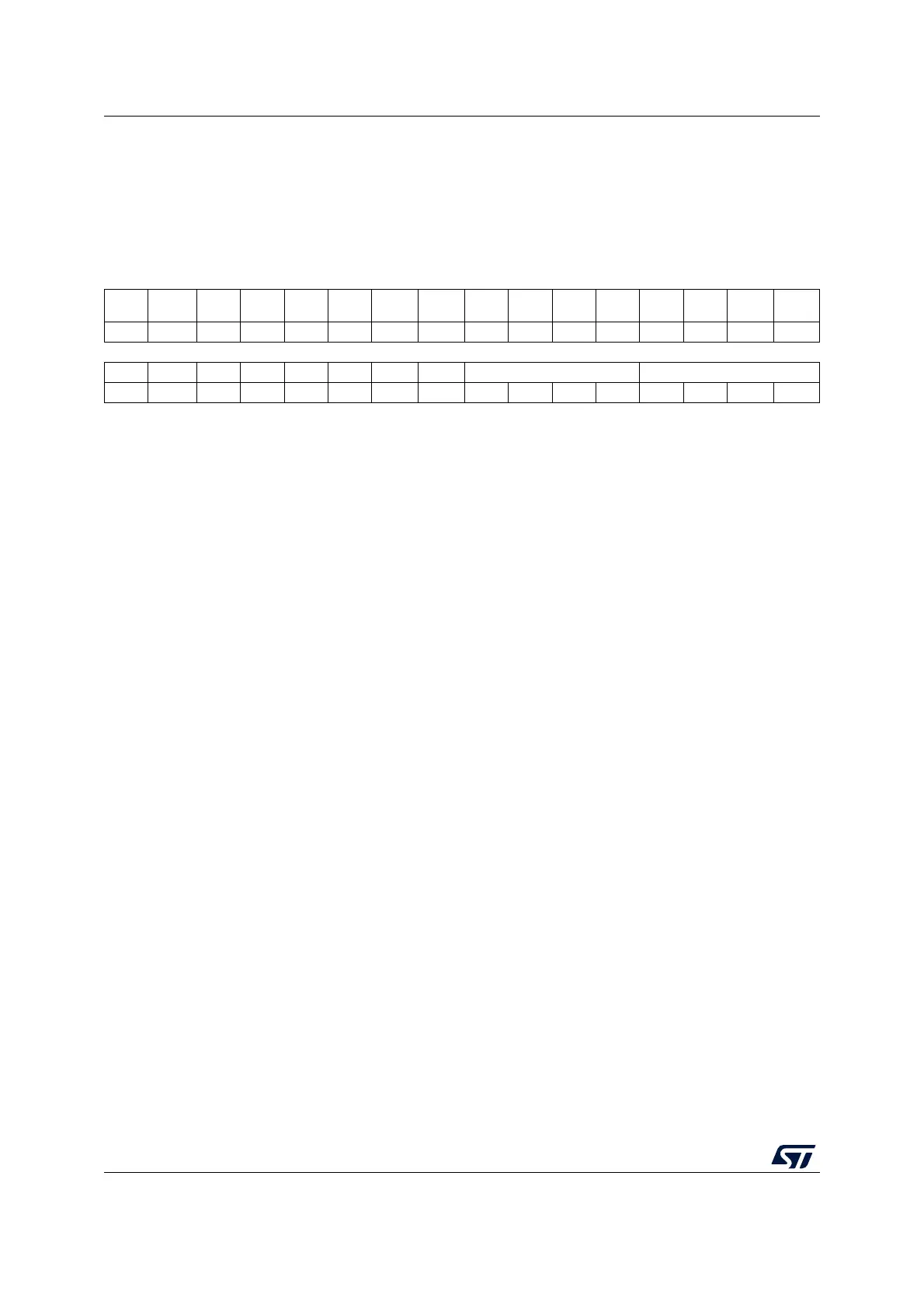

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

C2

HPREF

SHD

HPREF

rr

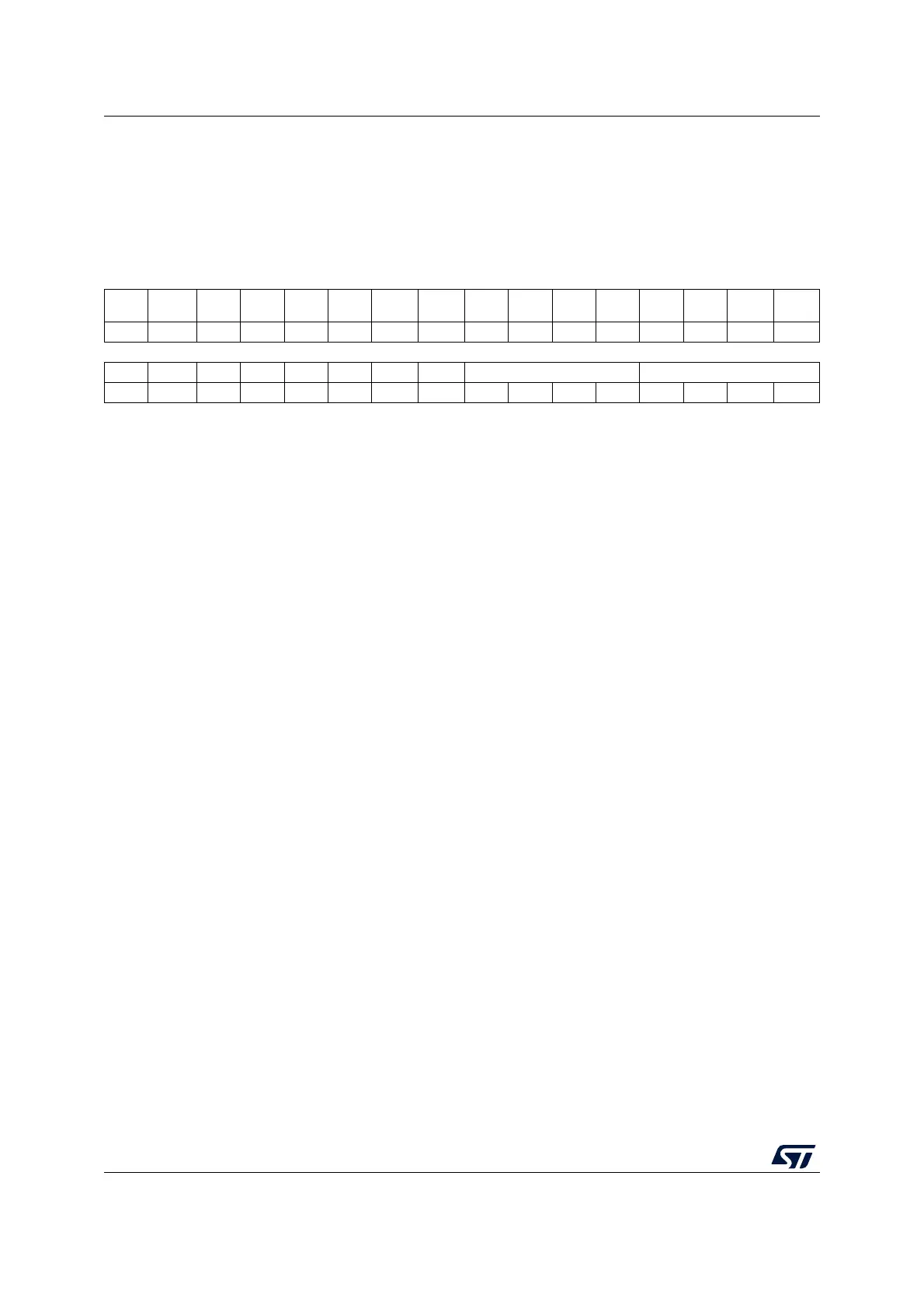

1514131211109 8 765432 1 0

Res. Res. Res. Res. Res. Res. Res. Res. C2HPRE[3:0] SHDHPRE[3:0]

rw rw rw rw rw rw rw rw

Bits 31:18 Reserved, must be kept at reset value.

Bit 17 C2HPREF: HCLK2 prescaler flag (CPU2)

This bit is set and cleared by hardware to acknowledge HCLK2 prescaler programming. It is

reset when a new prescaler value is programmed in C2HPRE[3:0]. This bit is set when the

programmed value is actually applied.

0: HCLK2 prescaler value not yet applied

1: HCLK2 prescaler value applied

Bit 16 SHDHPREF: HCLK3 shared prescaler flag (AHB3, Flash, SRAM1, and SRAM2)

This bit is set and cleared by hardware to acknowledge the shared HCLK3 prescaler

programming. It is reset when a new prescaler value is programmed in SHDHPRE[3:0]. This

bit is set when the programmed value is actually applied.

0: HCLK3 prescaler value not yet applied

1: HCLK3 prescaler value applied

Loading...

Loading...