Nested vectored interrupt controller (NVIC) RM0453

504/1461 RM0453 Rev 1

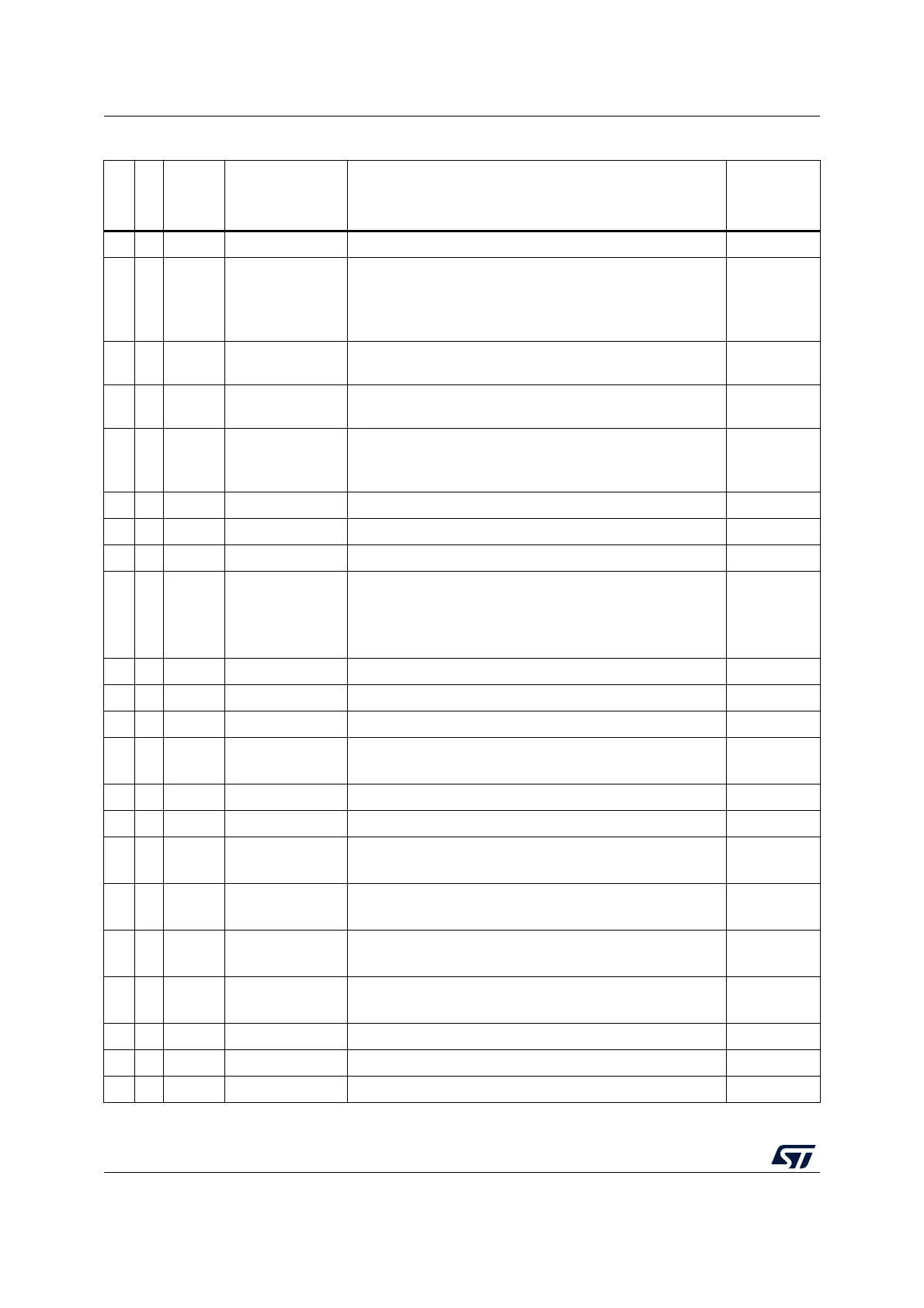

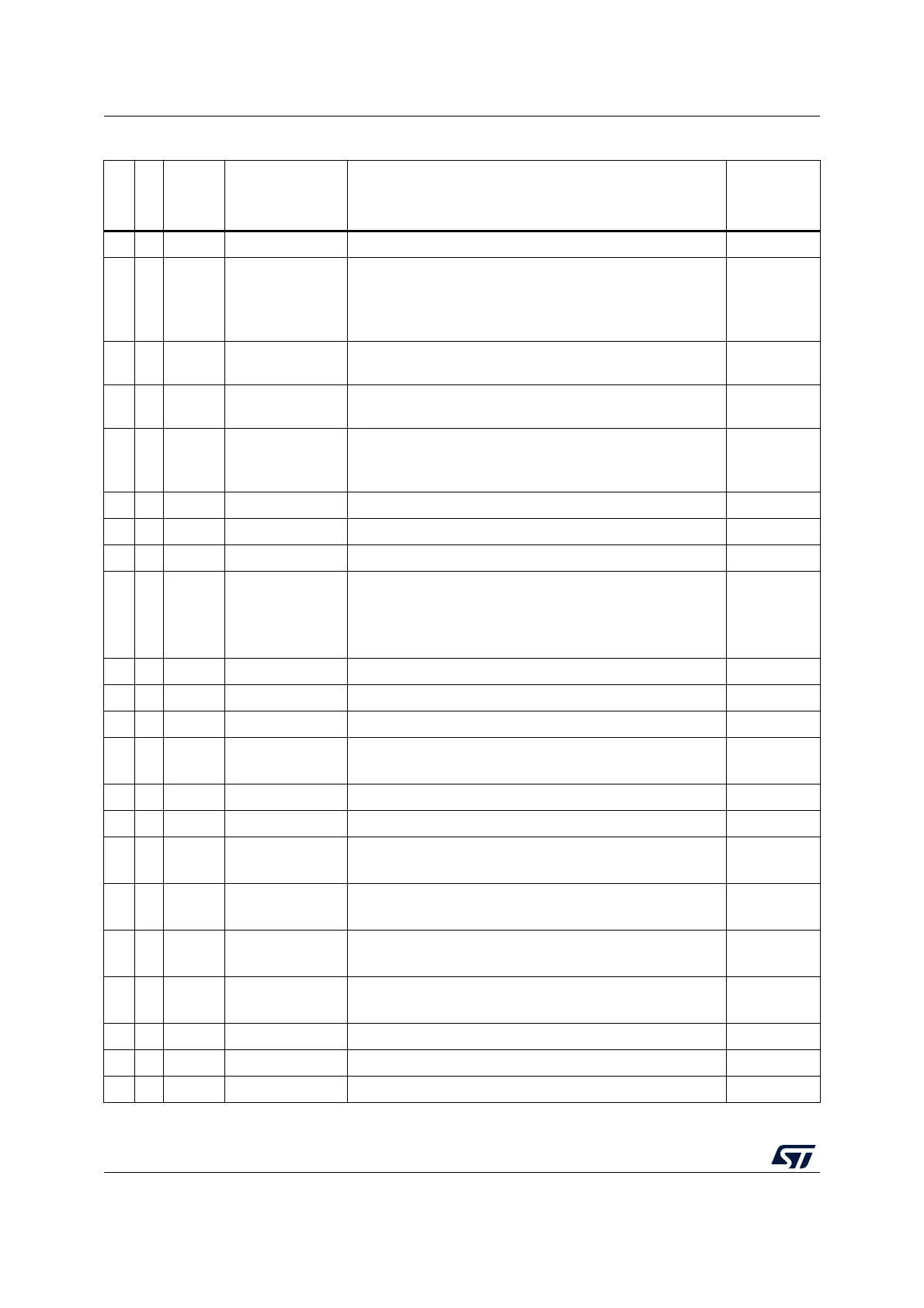

6 9 Settable EXTI[15:4] EXTI line 15:4 interrupt through EXTI[15:4] (C2IMR1[31:20]) 0x0000 0058

7 10 Settable

COMP,

ADC,

DAC

COMP1 and COMP2 interrupt through EXTI[22:21]

(C2IMR1[11])

ADC global interrupt (C2IMR1[12])

DAC global interrupt (C2IMR1[13])

0x0000 005C

8 11 Settable DMA1_CH[3:1]

DMA1 channel 3:1 secure and non-secure interrupt

(C2IMR2[2:0])

0x0000 0060

9 12 Settable DMA1_CH[7:4]

DMA1 channel 7:4 secure and non-secure interrupt

(C2IMR2[6:3])

0x0000 0064

10 13 Settable

DMA2_CH[7:1],

DMAMUX1_OVR

DMA2 channel 7:1 secure and non-secure interrupt

(C2IMR2[14:8])

DMAMUX1 overrun interrupt (C2IMR2[15])

0x0000 0068

11 14 Settable LPTIM1 LPtimer 1 global interrupt 0x0000 006C

12 15 Settable LPTIM2 LPtimer 2 global interrupt 0x0000 0070

13 16 Settable LPTIM3 LPtimer 3 global interrupt 0x0000 0074

14 17 Settable

TIM1_BRK,

TIM1_UP,

TIM1_TRG_COM,

TIM1_CC

Timer 1 break

Timer 1 update

Timer 1 trigger and communication

Timer 1 capture compare interrupt

0x0000 0078

15 18 Settable TIM2 Timer 2 global interrupt 0x0000 007C

16 19 Settable TIM16 Timer 16 global interrupt 0x0000 0080

17 20 Settable TIM17 Timer 17 global interrupt 0x0000 0084

18 21 Settable

IPCC_C2_RX_IT

IPCC_C2_TX_IT

IPCC CPU2 RX occupied interrupt

IPCC CPU2 TX free interrupt

0x0000 0088

19 22 Settable HSEM Semaphore interrupt 1 o CPU2 0x0000 008C

20 23 Settable True RNG True random number generator interrupt 0x0000 0090

21 24 Settable

AES

PKA

AES global interrupt (C2IMR1[10])

Private key accelerator interrupt (C2IMR1[8])

0x0000 0094

22 25 Settable

I2C1_EV

I2C1_ER

I2C1 event interrupt

I2C1 error interrupt

0x0000 0098

23 26 Settable

I2C2_EV

I2C2_ER

I2C2 event interrupt

I2C2 error interrupt

0x0000 009C

24 27 Settable

I2C3_EV

I2C3_ER

I2C3 event interrupt

I2C3 error interrupt

0x0000 00A0

25 28 Settable SPI1 SPI1 global interrupt 0x0000 00A4

26 29 Settable SPI2S2 SPI2S2 global interrupt 0x0000 00A8

27 30 Settable USART1 USART1 global interrupt 0x0000 00AC

Table 90. CPU2 vector table (continued)

Position

Priority

Type of

priority

Acronym Description

(1)(2)

Address

Loading...

Loading...