RM0453 Rev 1 505/1461

RM0453 Nested vectored interrupt controller (NVIC)

505

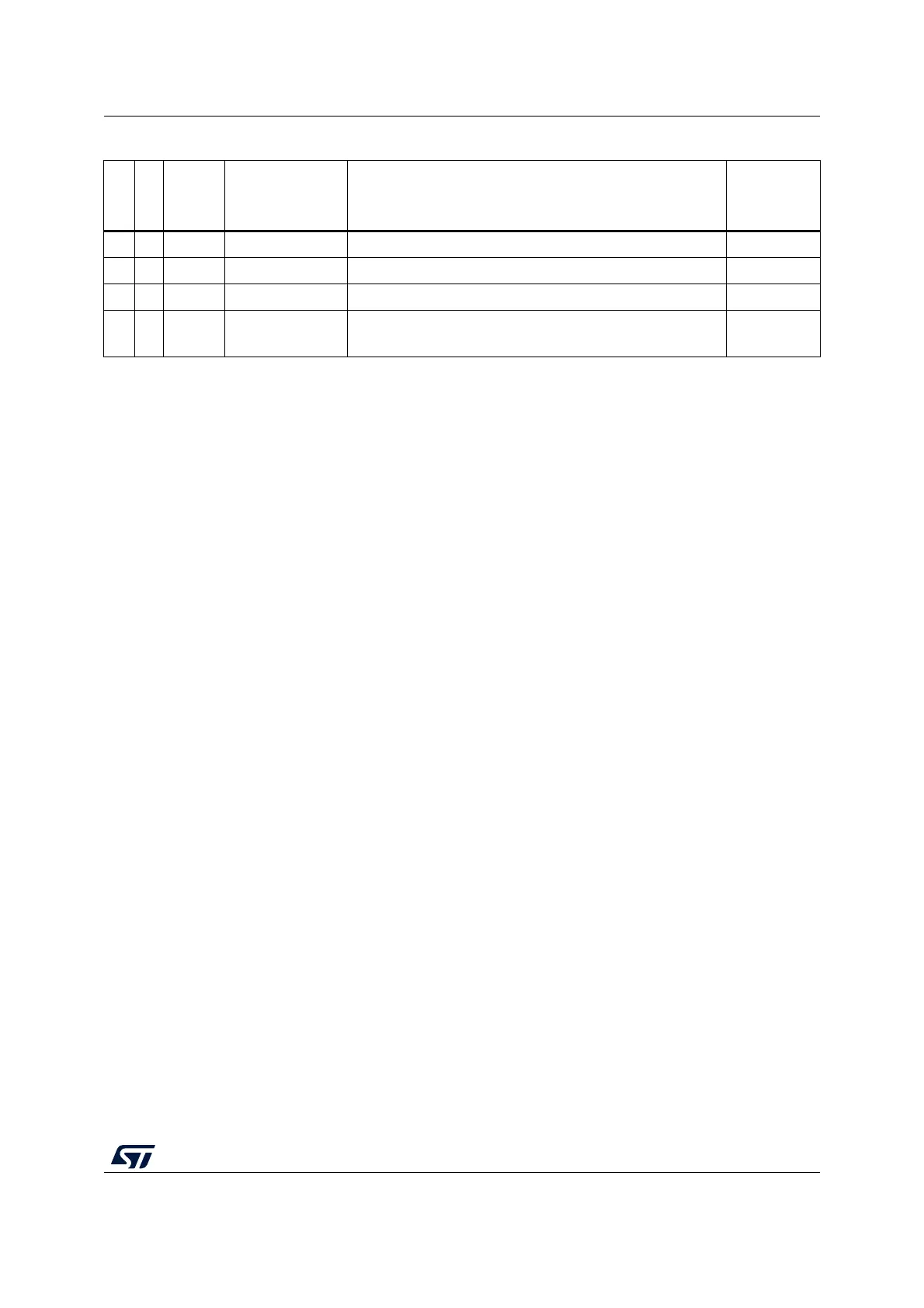

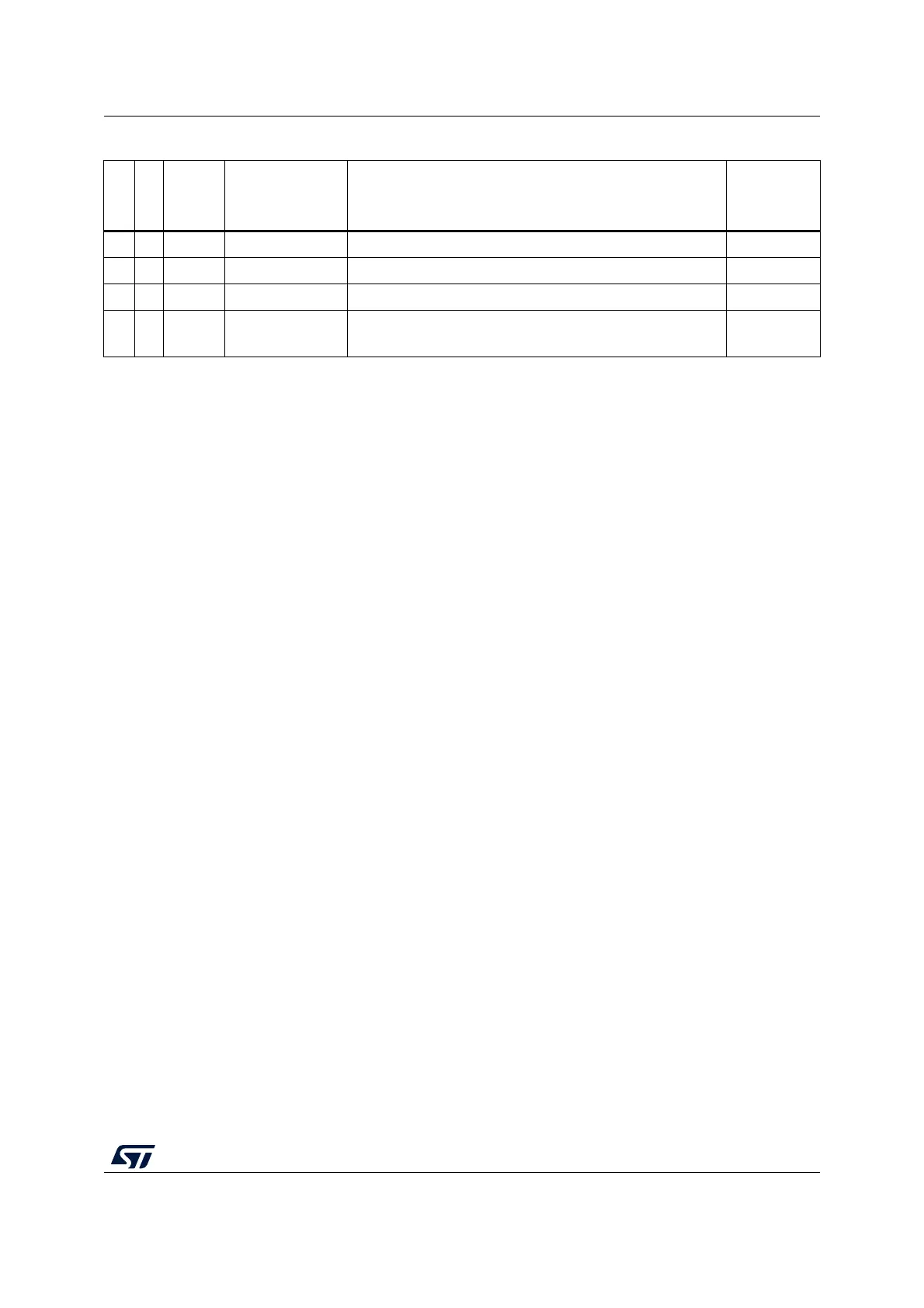

28 31 Settable USART2 USART2 global interrupt 0x0000 00B0

29 32 Settable LPUART1 LPUART1 global interrupt 0x0000 00B4

30 33 Settable SUBGHZSPI Sub-GHz radio SPI global interrupt 0x0000 00B8

31 34 Settable

Radio IRQ

Busy

Radio IRQs

RFBUSY interrupt through EXTI[45]

0x0000 00BC

1. C2IMRx[n] refer to the pre-mask bit[n] in SYSCFG_C2IMRx register.

2. EXTI[n] refer to the input event number [n] of the EXTI.

Table 90. CPU2 vector table (continued)

Position

Priority

Type of

priority

Acronym Description

(1)(2)

Address

Loading...

Loading...