CMS32L051 User Manual |Chapter 14 Serial interface IICA

www.mcu.com.cn 515 / 703

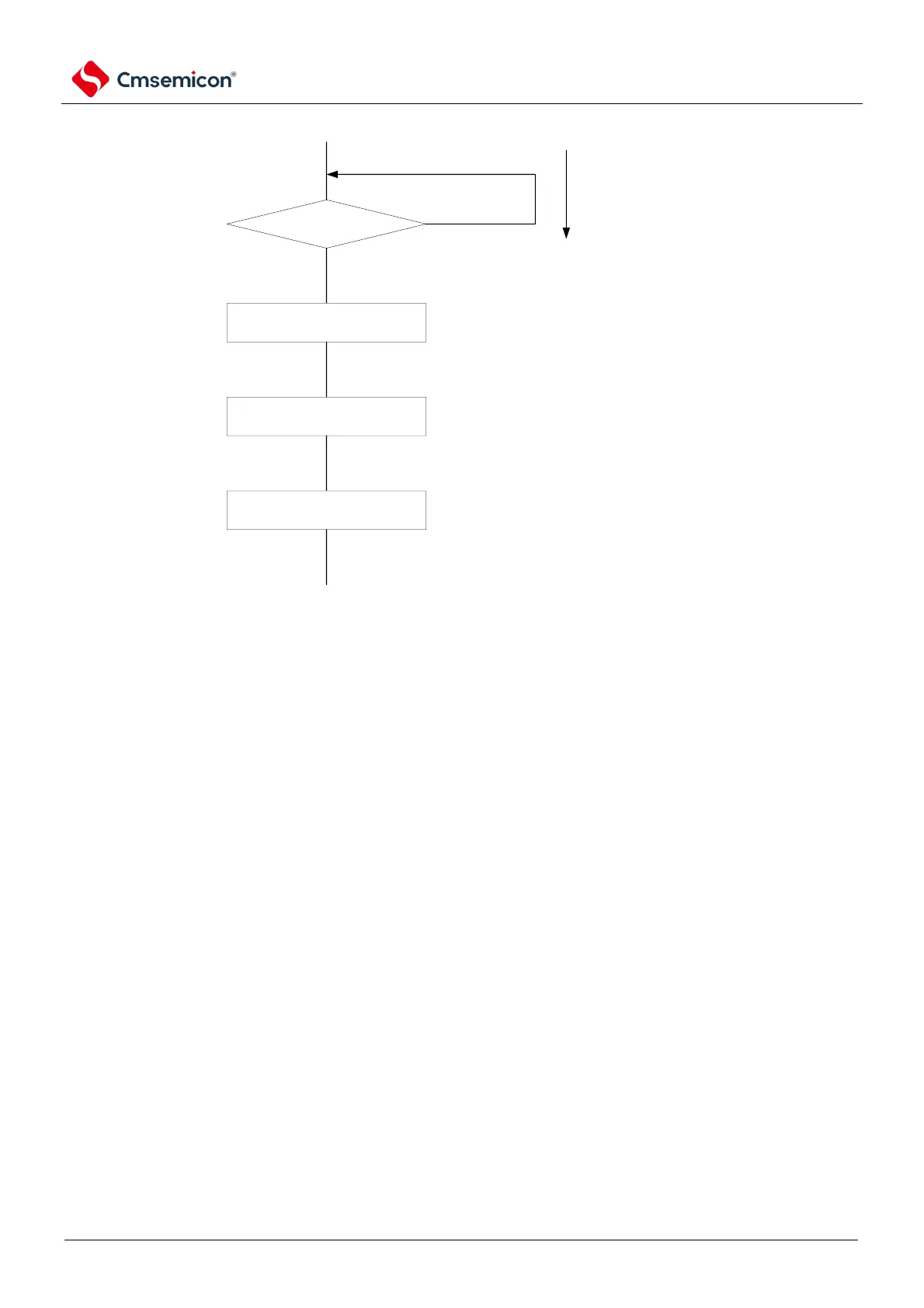

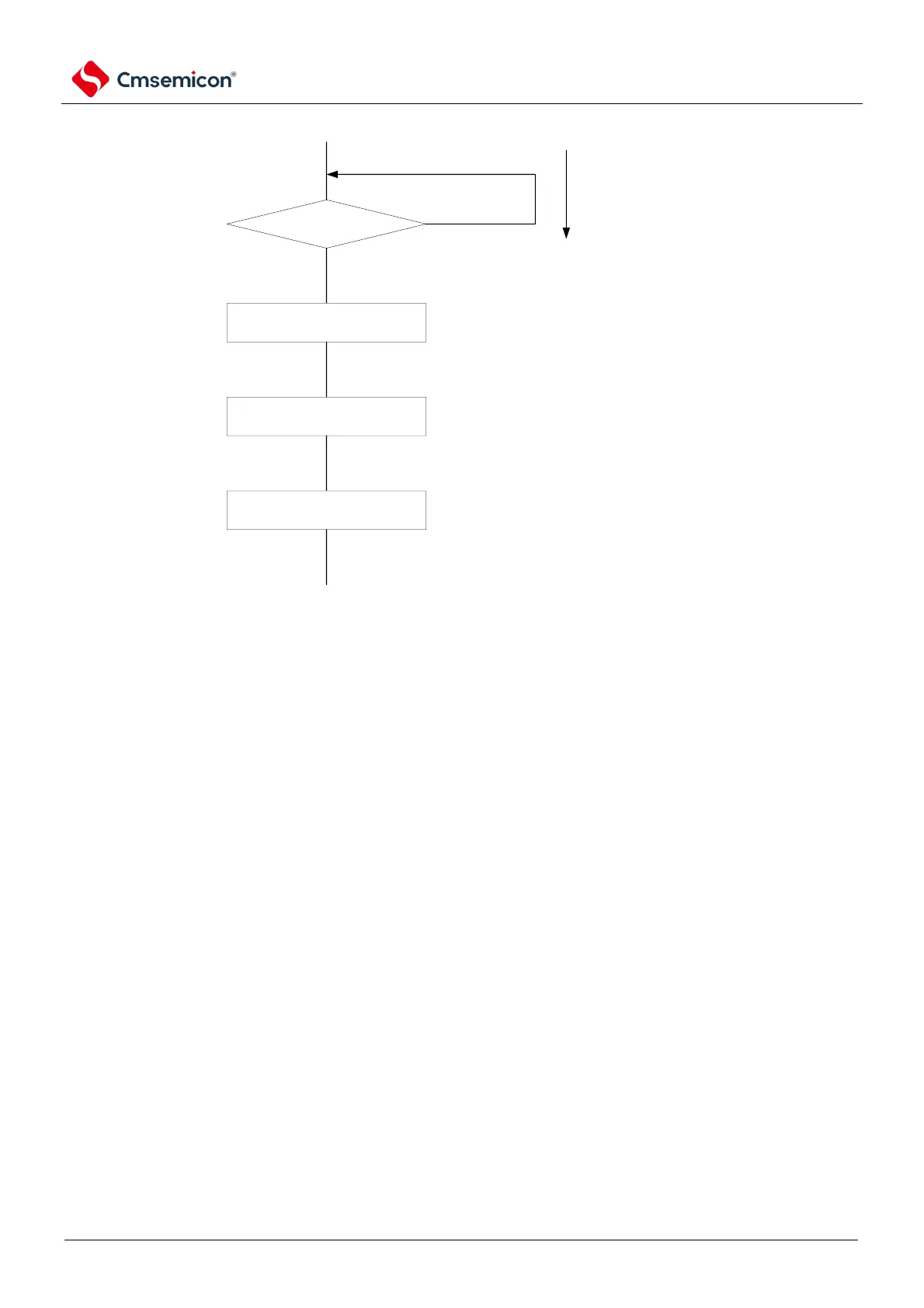

Figure 14-22 Flow when the WUPn bit is set to "0" by address matching (including receiving extension codes)

INTIICAn=1?

WUPn=0

wait

Read IICSn

Yes

No

deep sleep mode

state

wait for 5 fMCK clock.

after confirming serial interface IICA operation

status, process accordingly.

In addition to interrupt requests (INTIICAn) generated by the serial interface IICA, deep sleep mode must

be released through the following procedure.

The next time IIC communication is in operation with the master control device: Figure 14-23

The next time the IIC communication is in the case of the slave running for the device:

The case returned by INTIICAn interrupt: Same as Figure 14-22.

Cases returned by interrupt other than INTIICAn interrupt: The WUPn bit must be kept at "1" to continue

operation until the INTIICAn interrupt is generated.

Remark n=0

Loading...

Loading...