CMS32L051 User Manual |Chapter 14 Serial interface IICA

www.mcu.com.cn 518 / 703

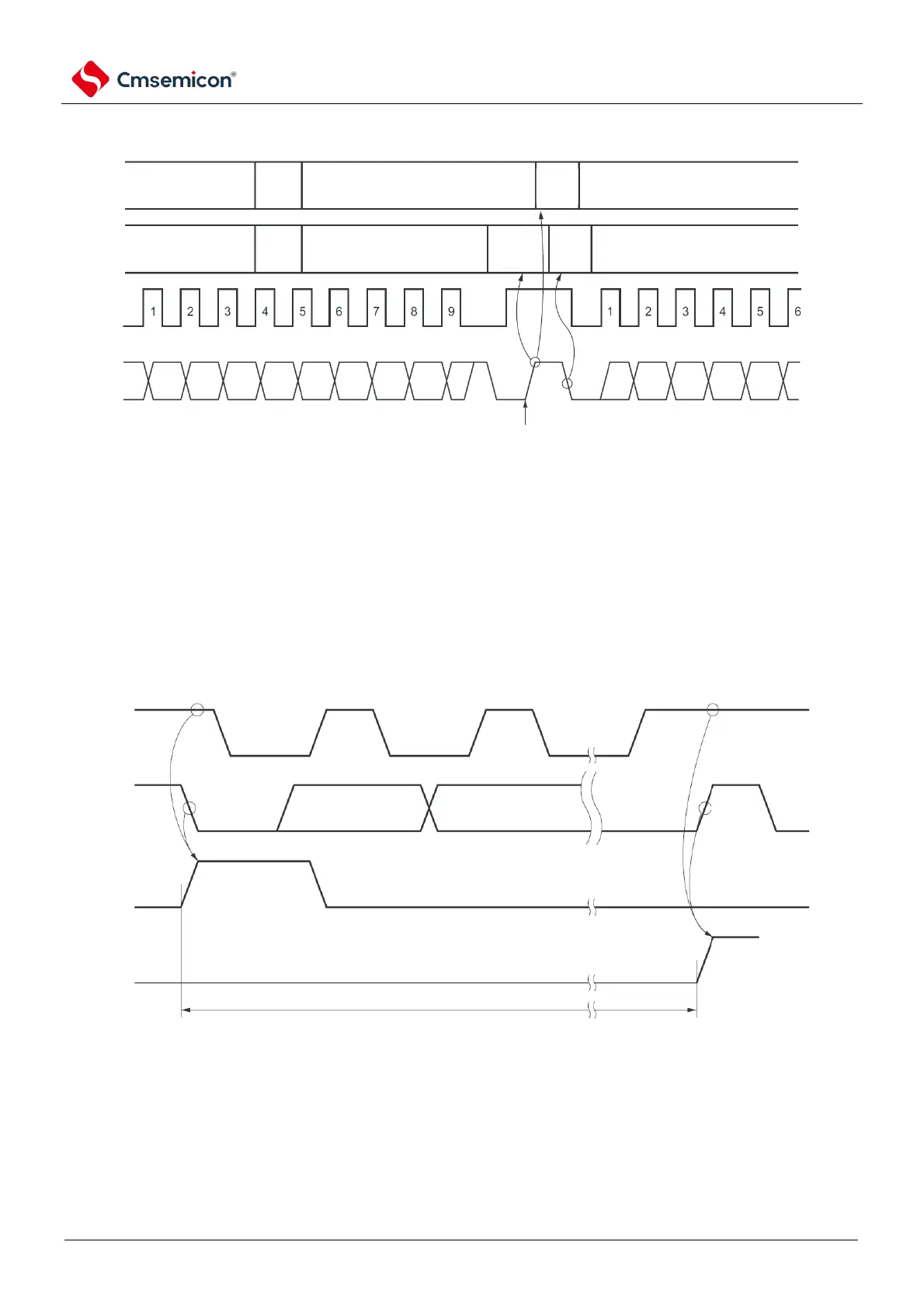

The timing of the communication reservation is shown in the following figure.

Figure 14-24 Timing of communication reservation

Note IICAn: IICA shift register n

STTn: bit1 of IICA control register n0 (IICCTLn0).

STDn: bit1 of IICA status register n (IICSn).

SPDn: bit0 of IICA status register n (IICSn).

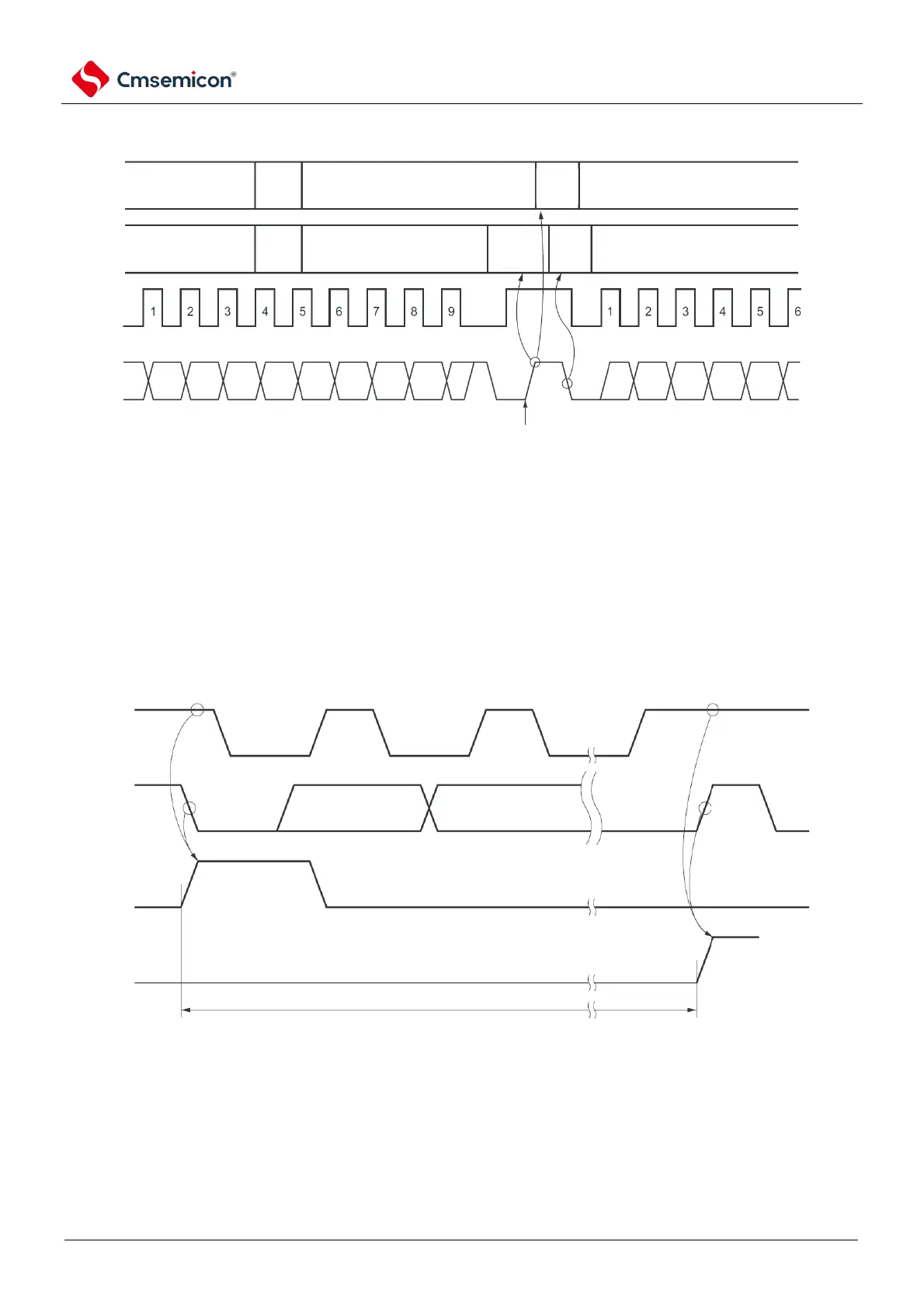

The communication reservation is accepted by the timing sequence shown in Figure 14-25. After bit 1

(STDn) of the IICA status register n (IICSn) becomes "1" and before the stop condition is detected, set bit 1

(STTn) of the IICA control register n0 (IICCTLn0) to "1 " for communication reservation.

Figure 14-25 Receiving timing of communication reservation

Loading...

Loading...