Secure digital input/output interface (SDIO) RM0390

1018/1328 RM0390 Rev 4

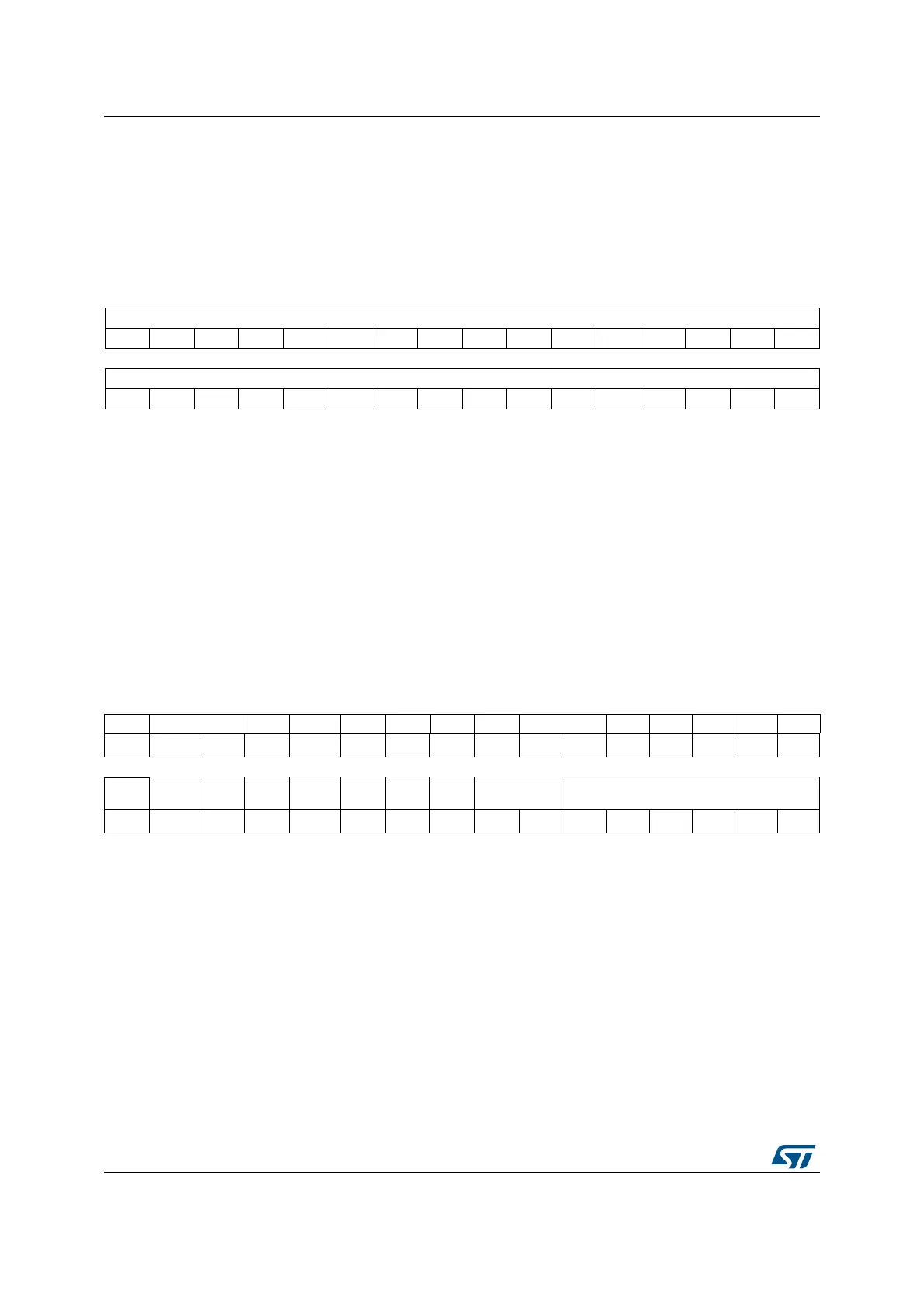

29.8.3 SDIO argument register (SDIO_ARG)

Address offset: 0x08

Reset value: 0x0000 0000

The SDIO_ARG register contains a 32-bit command argument, which is sent to a card as

part of a command message.

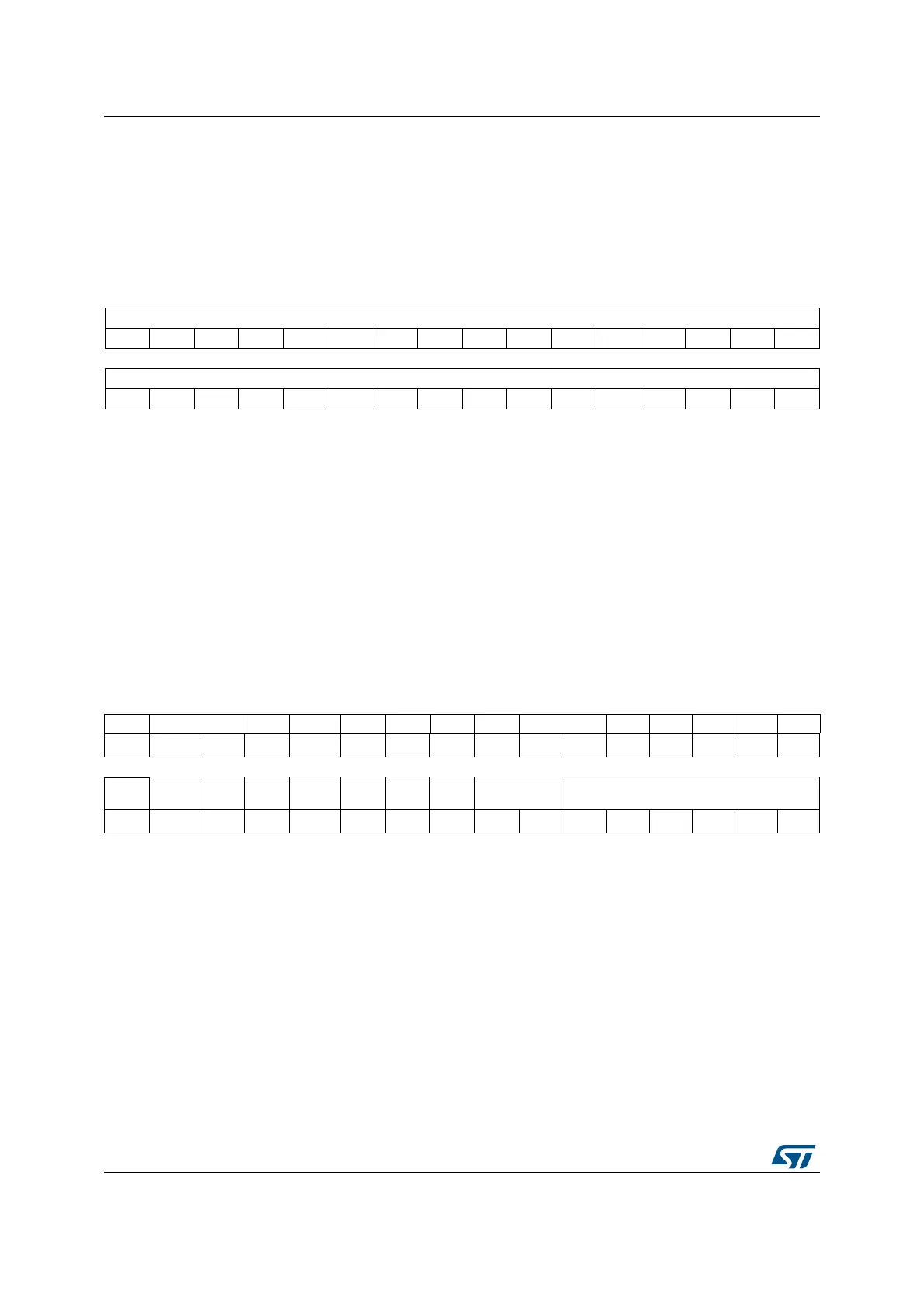

29.8.4 SDIO command register (SDIO_CMD)

Address offset: 0x0C

Reset value: 0x0000 0000

The SDIO_CMD register contains the command index and command type bits. The

command index is sent to a card as part of a command message. The command type bits

control the command path state machine (CPSM).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

CMDARG[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

1514131211109876543210

CMDARG[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 CMDARG: Command argument

Command argument sent to a card as part of a command message. If a command contains

an argument, it must be loaded into this register before writing a command to the command

register.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res.

SDIO

Suspend

CPSM

EN

WAIT

PEND

WAIT

INT

WAITRESP CMDINDEX

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:12 Reserved, must be kept at reset value.

Bit 11 SDIOSuspend: SD I/O suspend command

If this bit is set, the command to be sent is a suspend command (to be used only with SDIO

card).

Bit 10 CPSMEN: Command path state machine (CPSM) Enable bit

If this bit is set, the CPSM is enabled.

Bit 9 WAITPEND: CPSM Waits for ends of data transfer (CmdPend internal signal).

If this bit is set, the CPSM waits for the end of data transfer before it starts sending a

command. This feature is available only with Stream data transfer mode

SDIO_DCTRL[2] = 1.

Loading...

Loading...