Analog-to-digital converter (ADC) RM0390

386/1328 RM0390 Rev 4

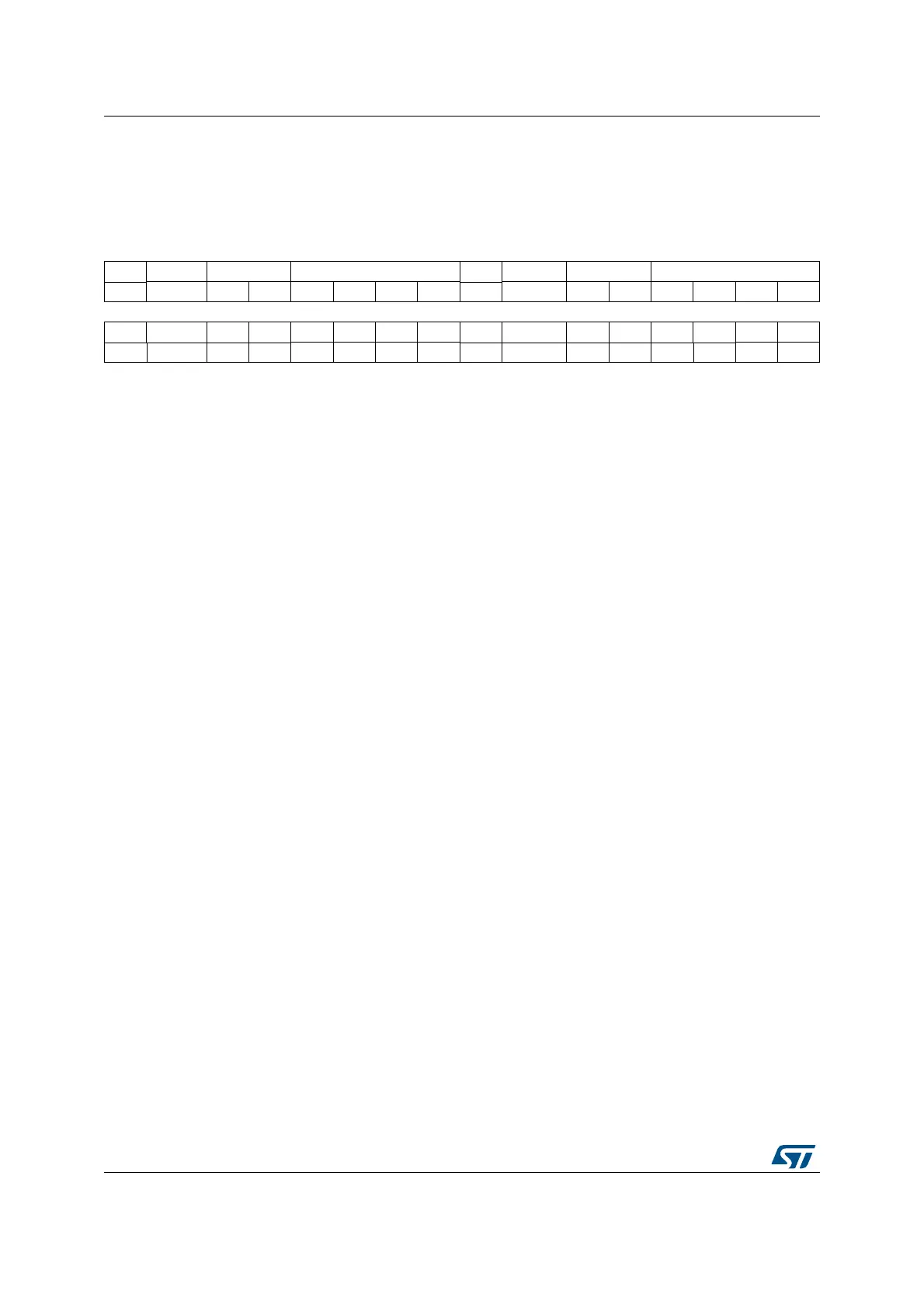

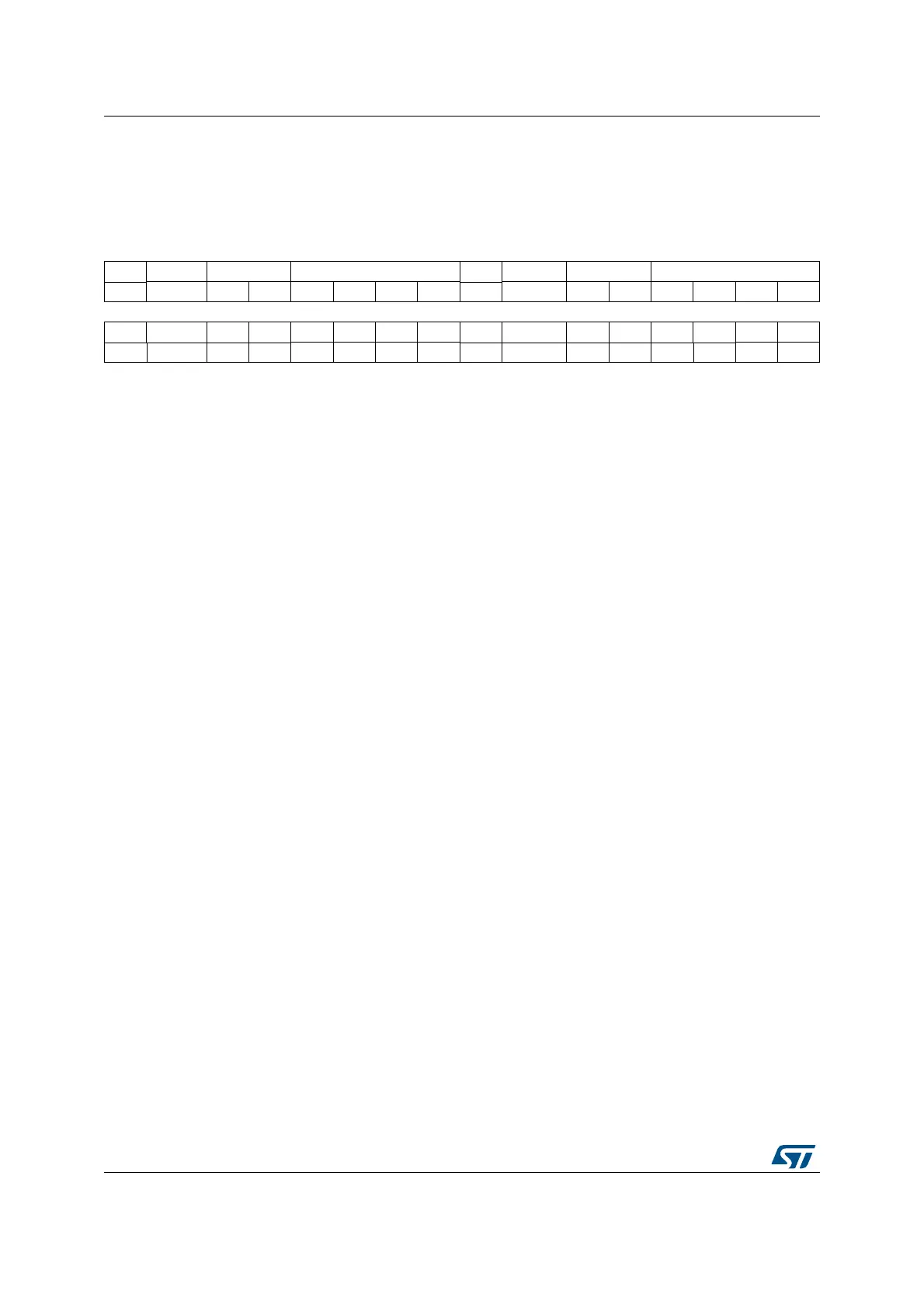

13.13.3 ADC control register 2 (ADC_CR2)

Address offset: 0x08

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. SWSTART EXTEN EXTSEL[3:0] Res. JSWSTART JEXTEN JEXTSEL[3:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw

15 14 13121110987 6 543210

Res. Res. Res. Res. ALIGN EOCS DDS DMA Res. Res. Res. Res. Res. Res. CONT ADON

rw rw rw rw rw rw

Bit 31 Reserved, must be kept at reset value.

Bit 30 SWSTART: Start conversion of regular channels

This bit is set by software to start conversion and cleared by hardware as soon as the

conversion starts.

0: Reset state

1: Starts conversion of regular channels

Note: This bit can be set only when ADON = 1 otherwise no conversion is launched.

Bits 29:28 EXTEN: External trigger enable for regular channels

These bits are set and cleared by software to select the external trigger polarity and enable

the trigger of a regular group.

00: Trigger detection disabled

01: Trigger detection on the rising edge

10: Trigger detection on the falling edge

11: Trigger detection on both the rising and falling edges

Bits 27:24 EXTSEL[3:0]: External event select for regular group

These bits select the external event used to trigger the start of conversion of a regular group:

0000: Timer 1 CC1 event

0001: Timer 1 CC2 event

0010: Timer 1 CC3 event

0011: Timer 2 CC2 event

0100: Timer 2 CC3 event

0101: Timer 2 CC4 event

0110: Timer 2 TRGO event

0111: Timer 3 CC1 event

1000: Timer 3 TRGO event

1001: Timer 4 CC4 event

1010: Timer 5 CC1 event

1011: Timer 5 CC2 event

1100: Timer 5 CC3 event

1101: Timer 8 CC1 event

1110: Timer 8 TRGO event

1111: EXTI line 11

Bit 23 Reserved, must be kept at reset value.

Bit 22 JSWSTART: Start conversion of injected channels

This bit is set by software and cleared by hardware as soon as the conversion starts.

0: Reset state

1: Starts conversion of injected channels

Note: This bit can be set only when ADON = 1 otherwise no conversion is launched.

Loading...

Loading...