RM0390 Rev 4 1157/1328

RM0390 USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS)

1264

31.15.30 OTG host channel x DMA address register (OTG_HCDMAx)

(x = 0..15, where x = Channel number)

Address offset: 0x514 + (x * 0x20)

Reset value: 0x0000 0000

31.15.31 Device-mode registers

These registers must be programmed every time the core changes to device mode

Bit 31 Reserved, must be kept at reset value.

Bits 30:29 DPID[1:0]: Data PID

The application programs this field with the type of PID to use for the initial transaction. The

host maintains this field for the rest of the transfer.

00: DATA0

01: DATA2

10: DATA1

11: SETUP (control) / reserved[FS]MDATA[HS] (non-control)

Bits 28:19 PKTCNT[9:0]: Packet count

This field is programmed by the application with the expected number of packets to be

transmitted (OUT) or received (IN).

The host decrements this count on every successful transmission or reception of an OUT/IN

packet. Once this count reaches zero, the application is interrupted to indicate normal

completion.

Bits 18:0 XFRSIZ[18:0]: Transfer size

For an OUT, this field is the number of data bytes the host sends during the transfer.

For an IN, this field is the buffer size that the application has reserved for the transfer. The

application is expected to program this field as an integer multiple of the maximum packet

size for IN transactions (periodic and non-periodic).

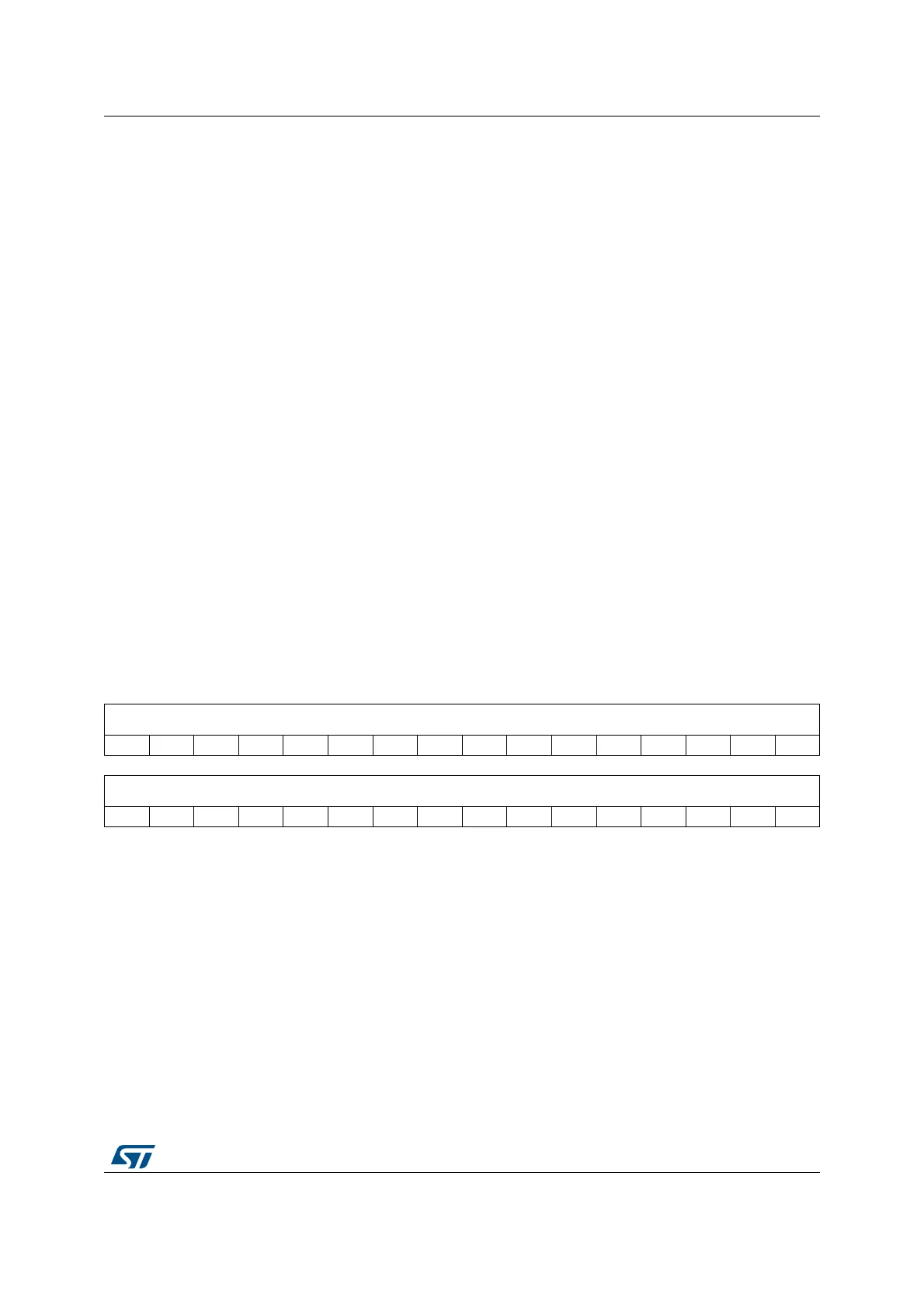

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DMAADDR[31:16]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

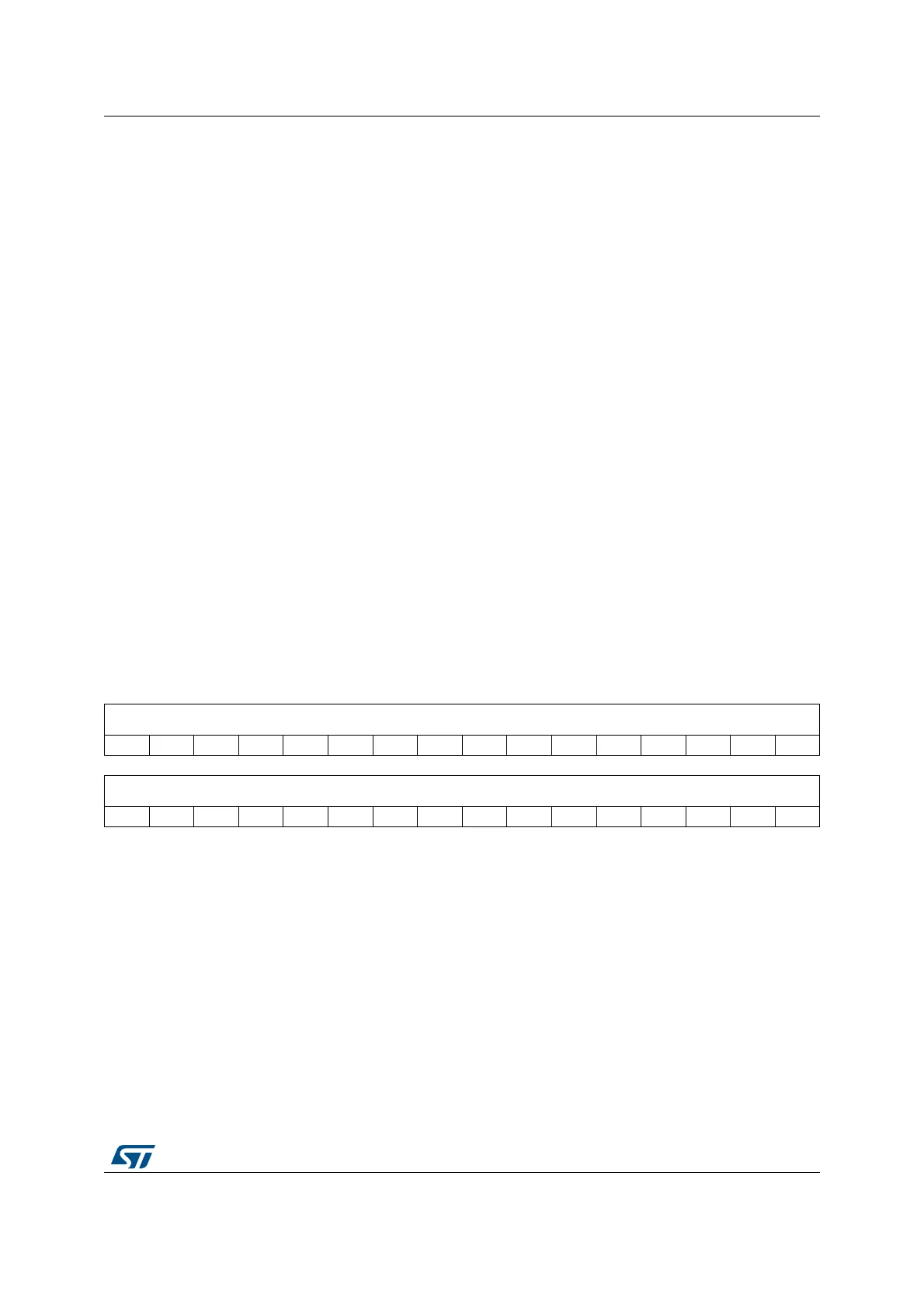

1514131211109876543210

DMAADDR[15:0]

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:0 DMAADDR[31:0]: DMA address

This field holds the start address in the external memory from which the data for the endpoint

must be fetched or to which it must be stored. This register is incremented on every AHB

transaction.

Loading...

Loading...