Reset and clock control (RCC) RM0390

118/1328 RM0390 Rev 4

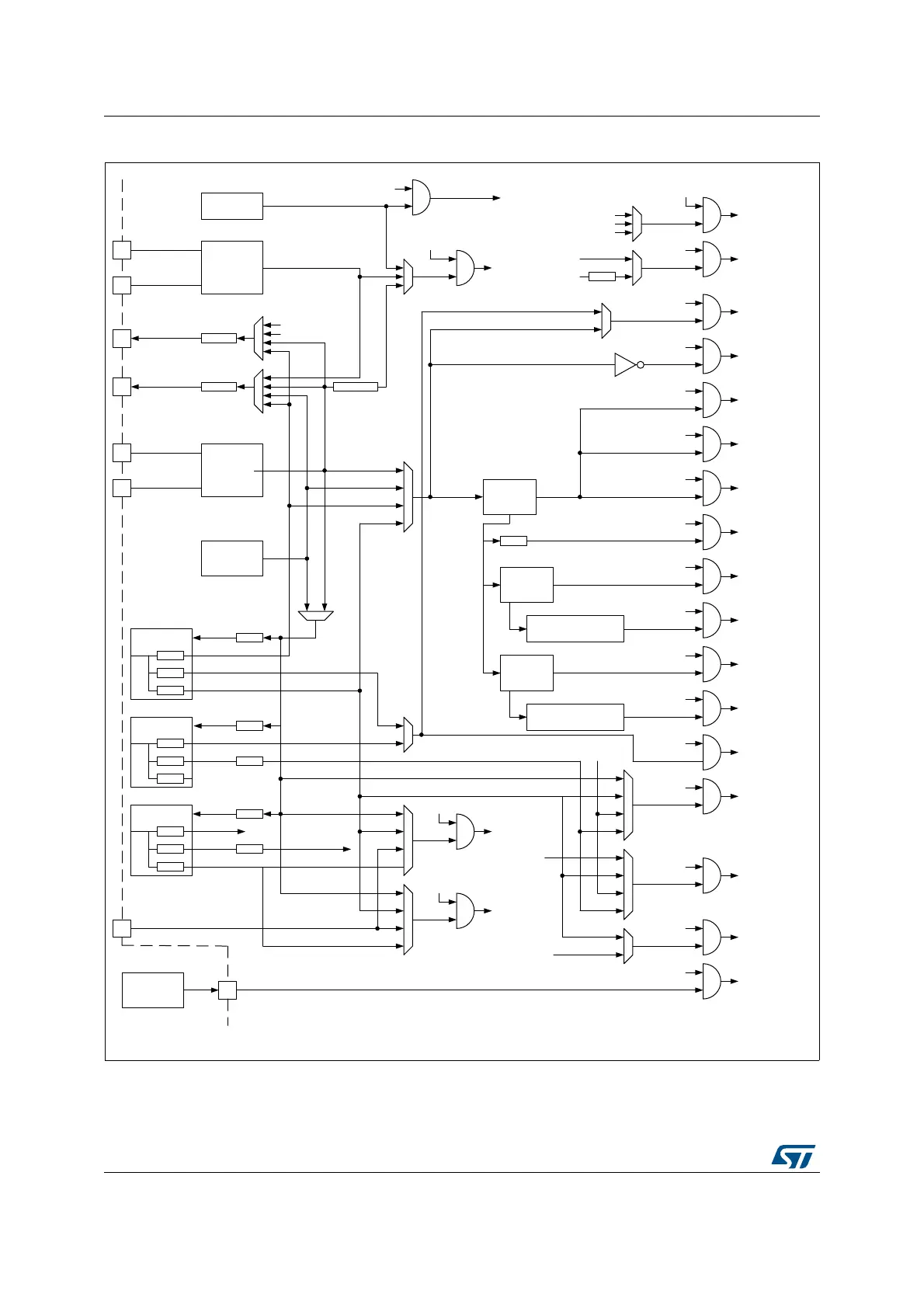

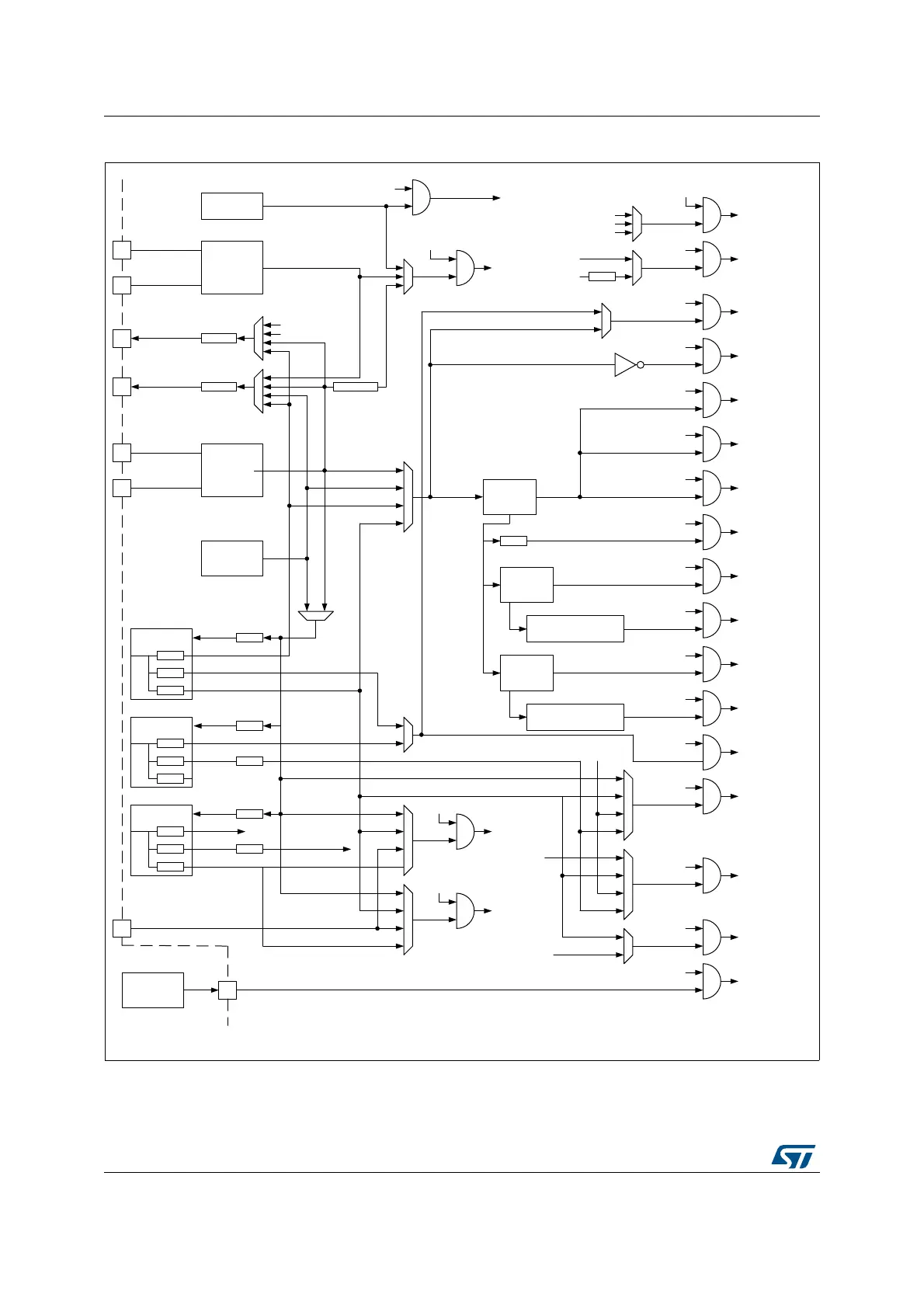

Figure 14. Clock tree

1. For full details about the internal and external clock source characteristics, refer to the Electrical

characteristics section in the device datasheet.

2. When TIMPRE bit of the RCC_DCKCFGR register is reset, if APBx prescaler is 1, then TIMxCLK = PCLKx,

06Y9

0&2

ĺ

6<6&/.

3//,6

ĺ

0&2

ĺ

0+]

+6,5&

+6,

3//

3//&/.

3//4

3//5

0

3

4

5

3//6$,

3//6$,3

3//6$,4

0

3

4

5

',9

3//,6

3//,63

3//,65

0

3

4

5

',9

3//,6B6$,&/.

3//5

86%3+<

ĺ0+]

27*B+6B6&/

,6

FORFNV

,6B&.,1

,6

FORFNV

$+%

35(6&

+6,

6<6&/.

3&/.

3HULSKHUDO

FORFNHQDEOH

)03,&

FORFN

+'0,&(&

FORFN

6',2

FORFN

3RZHUFWUO

FORFN

&38

FORFN

)&/.&RUWH[

IUHHUXQQLQJFORFN

$+%SHULSKHUDO

FORFNV

6\V7LFN

FORFN

$3%SHULSKHUDO

FORFNV

$3%WLPHU

FORFNV

$3%SHULSKHUDO

FORFNV

$3%WLPHU

FORFNV

LI$3%SUHVF [

HOVH [

$3%

35(6&

86%+6

8/3,FORFN

63',)5;,1

FORFN

3//,63

3//,6B6$,&/.

86%0+]

FORFN

6$,FORFN

6$,FORFN

LI$3%SUHVF [

HOVH [

$3%

35(6&

QRWGHHSVOHHS

QRWVOHHSRUGHHSVOHHS

+6(

+6,

3//&/.

3//5

6<6&/.

6\VWHP

FORFN

/6(

+6(B57&

/6(

+6,

/6,5&

N+]

/6,

(QDEOH

ZDWFKGRJ

,:'*&/.

57&$:8HQDEOH

57&$:8

FORFN

3//&/.

+6(

/(626&

N+]

26&B,1

26&B287

0+]

+6(26&

26&B,1

26&B287

&ORFN

HQDEOH

3HULSKHUDO

FORFNHQDEOH

3HULSKHUDO

FORFNHQDEOH

3HULSKHUDO

FORFNHQDEOH

3HULSKHUDO

FORFNHQDEOH

3HULSKHUDO

FORFNHQDEOH

FORFNHQDEOH

&ORFN

HQDEOH

,6B&.,1

&ORFNHQDEOH

&ORFNHQDEOH

&ORFN

HQDEOH

&ORFN

HQDEOH

&ORFN

HQDEOH

&ORFN

HQDEOH

&ORFN

HQDEOH

Loading...

Loading...