Digital camera interface (DCMI) RM0390

442/1328 RM0390 Rev 4

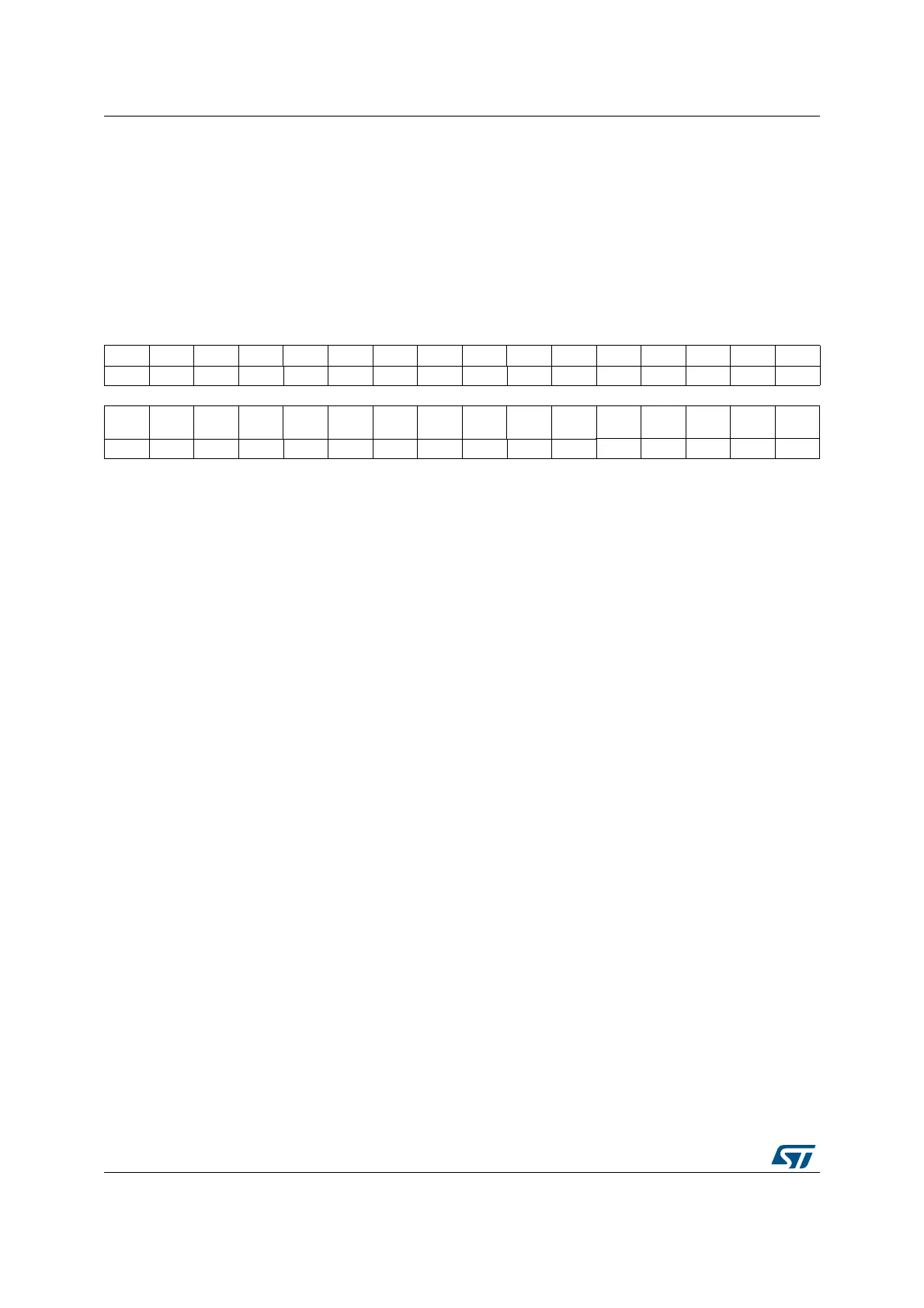

15.7.5 DCMI masked interrupt status register (DCMI_MIS)

This DCMI_MIS register is a read-only register. When read, it returns the current masked

status value (depending on the value in DCMI_IER) of the corresponding interrupt. A bit in

this register is set if the corresponding enable bit in DCMI_IER is set and the corresponding

bit in DCMI_RIS is set.

Address offset: 0x10

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

LINE

_MIS

VSYNC

_MIS

ERR

_MIS

OVR

_MIS

FRAME

_MIS

rrrrr

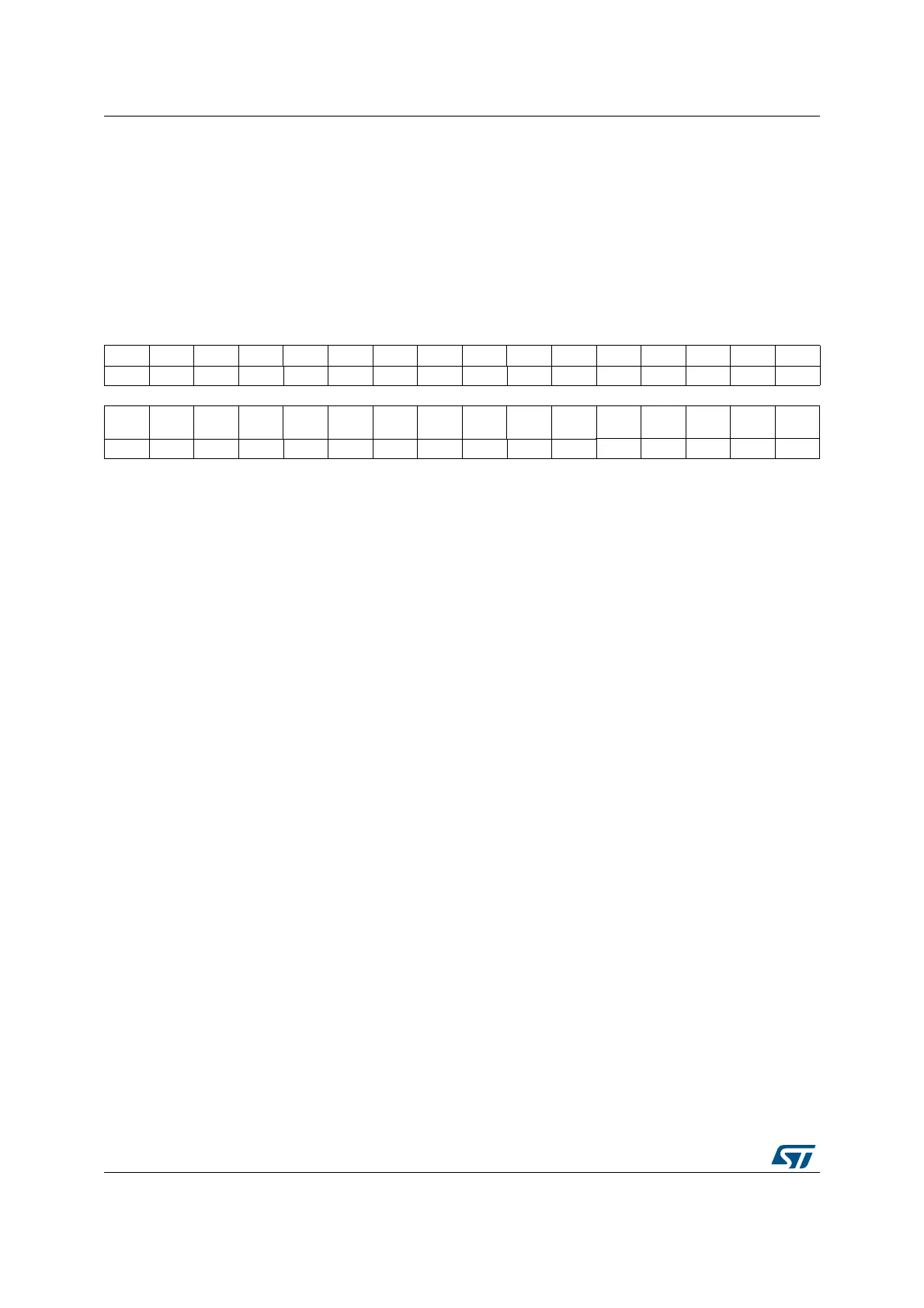

Bits 31:5 Reserved, must be kept at reset value.

Bit 4 LINE_MIS: Line masked interrupt status

This bit gives the status of the masked line interrupt

0: No interrupt generation when the line is received

1: An Interrupt is generated when a line has been completely received and the

LINE_IE bit is set in DCMI_IER.

Bit 3 VSYNC_MIS: VSYNC masked interrupt status

This bit gives the status of the masked VSYNC interrupt

0: No interrupt is generated on DCMI_VSYNC transitions

1: An interrupt is generated on each DCMI_VSYNC transition from the inactive

to the active state and the VSYNC_IE bit is set in DCMI_IER.

The active state of the DCMI_VSYNC signal is defined by the VSPOL bit.

Bit 2 ERR_MIS: Synchronization error masked interrupt status

This bit gives the status of the masked synchronization error interrupt

0: No interrupt is generated on a synchronization error

1: An interrupt is generated if the embedded synchronization codes are not

received in the correct order and the ERR_IE bit in DCMI_IER is set.

Note: This bit is available only in embedded synchronization mode.

Bit 1 OVR_MIS: Overrun masked interrupt status

This bit gives the status of the masked overflow interrupt

0: No interrupt is generated on overrun

1: An interrupt is generated if the DMA was not able to transfer the last data

before new data (32-bit) are received and the OVR_IE bit is set in DCMI_IER.

Bit 0 FRAME_MIS: Capture complete masked interrupt status

This bit gives the status of the masked capture complete interrupt

0: No interrupt is generated after a complete capture

1: An interrupt is generated at the end of each received frame/crop window (in

crop mode) and the FRAME_IE bit is set in DCMI_IER.

Loading...

Loading...