Digital camera interface (DCMI) RM0390

426/1328 RM0390 Rev 4

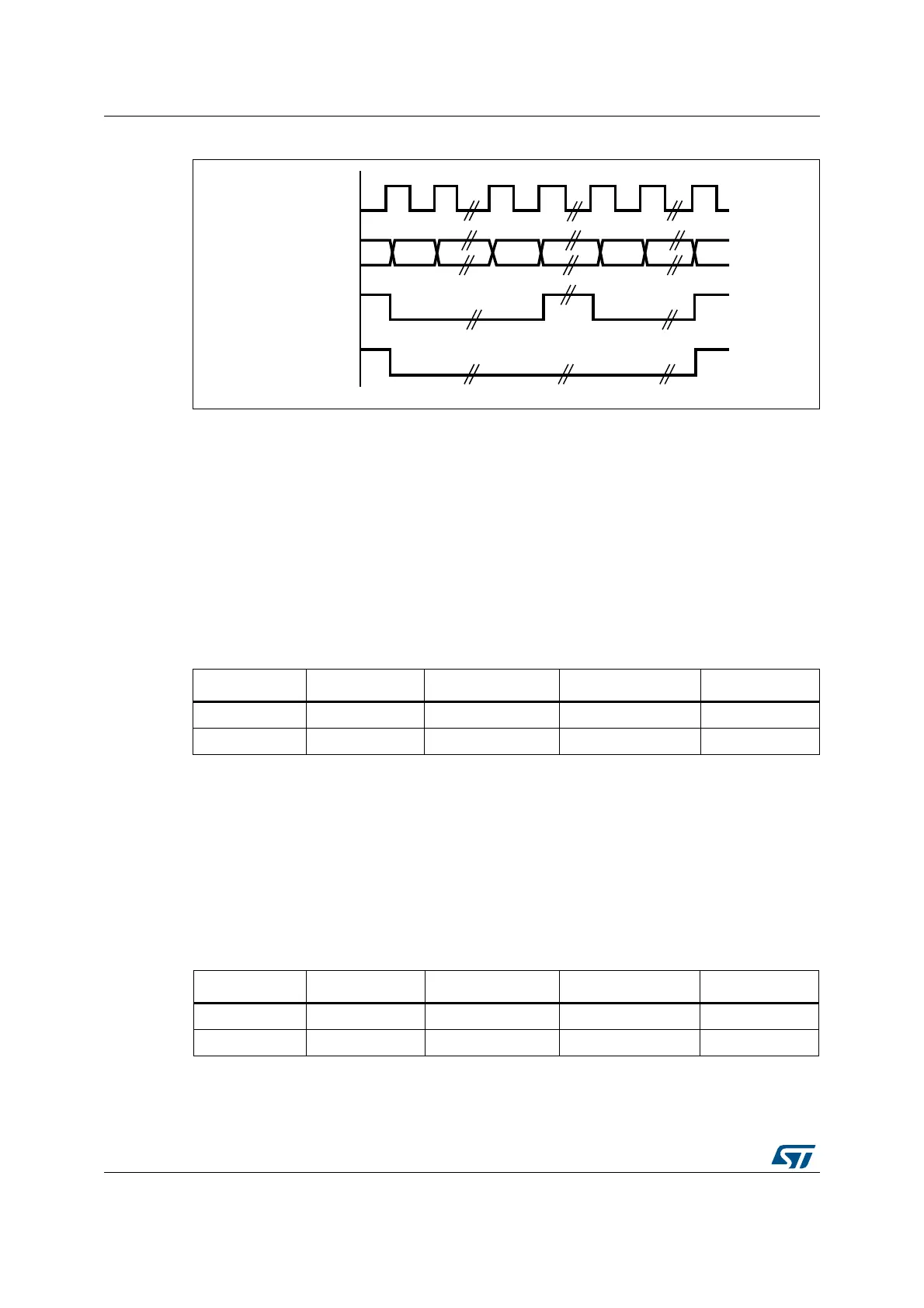

Figure 103. DCMI signal waveforms

1. The capture edge of DCMI_PIXCLK is the falling edge, the active state of DCMI_HSYNC and

DCMI_VSYNC is 1.

2. DCMI_HSYNC and DCMI_VSYNC can change states at the same time.

8-bit data

When EDM[1:0] in DCMI_CR are programmed to “00” the interface captures 8 LSBs at its

input (DCMI_D[0:7]) and stores them as 8-bit data. The DCMI_D[13:8] inputs are ignored. In

this case, to capture a 32-bit word, the camera interface takes four pixel clock cycles.

The first captured data byte is placed in the LSB position in the 32-bit word and the 4

th

captured data byte is placed in the MSB position in the 32-bit word. Table 97 gives an

example of the positioning of captured data bytes in two 32-bit words.

10-bit data

When EDM[1:0] in DCMI_CR are programmed to “01”, the camera interface captures 10-bit

data at its input DCMI_D[0..9] and stores them as the 10 least significant bits of a 16-bit

word. The remaining most significant bits in the DCMI_DR register (bits 11 to 15) are

cleared to zero. So, in this case, a 32-bit data word is made up every two pixel clock cycles.

The first captured data are placed in the LSB position in the 32-bit word and the 2

nd

captured data are placed in the MSB position in the 32-bit word as shown in Table 98.

Table 97. Positioning of captured data bytes in 32-bit words (8-bit width)

Byte address 31:24 23:16 15:8 7:0

0D

n+3

[7:0] D

n+2

[7:0] D

n+1

[7:0] D

n

[7:0]

4D

n+7

[7:0] D

n+6

[7:0] D

n+5

[7:0] D

n+4

[7:0]

Table 98. Positioning of captured data bytes in 32-bit words (10-bit width)

Byte address 31:26 25:16 15:10 9:0

00D

n+1

[9:0] 0 D

n

[9:0]

40D

n+3

[9:0] 0 D

n+2

[9:0]

$#-)?0)8#,+

$#-)?$2;=

$#-)?(39.#

$#-)?639.#

AIB

Loading...

Loading...