Fast-mode Plus Inter-integrated circuit (FMPI2C) interface RM0390

742/1328 RM0390 Rev 4

23.7 FMPI2C registers

Refer to Section 1.1 on page 51 for a list of abbreviations used in register descriptions.

The peripheral registers are accessed by words (32-bit).

23.7.1 Control register 1 (FMPI2C_CR1)

Address offset: 0x00

Reset value: 0x0000 0000

Access: No wait states, except if a write access occurs while a write access to this register is

ongoing. In this case, wait states are inserted in the second write access until the previous

one is completed. The latency of the second write access can be up to 2 x PCLK1 + 6 x

FMPI2CCLK.

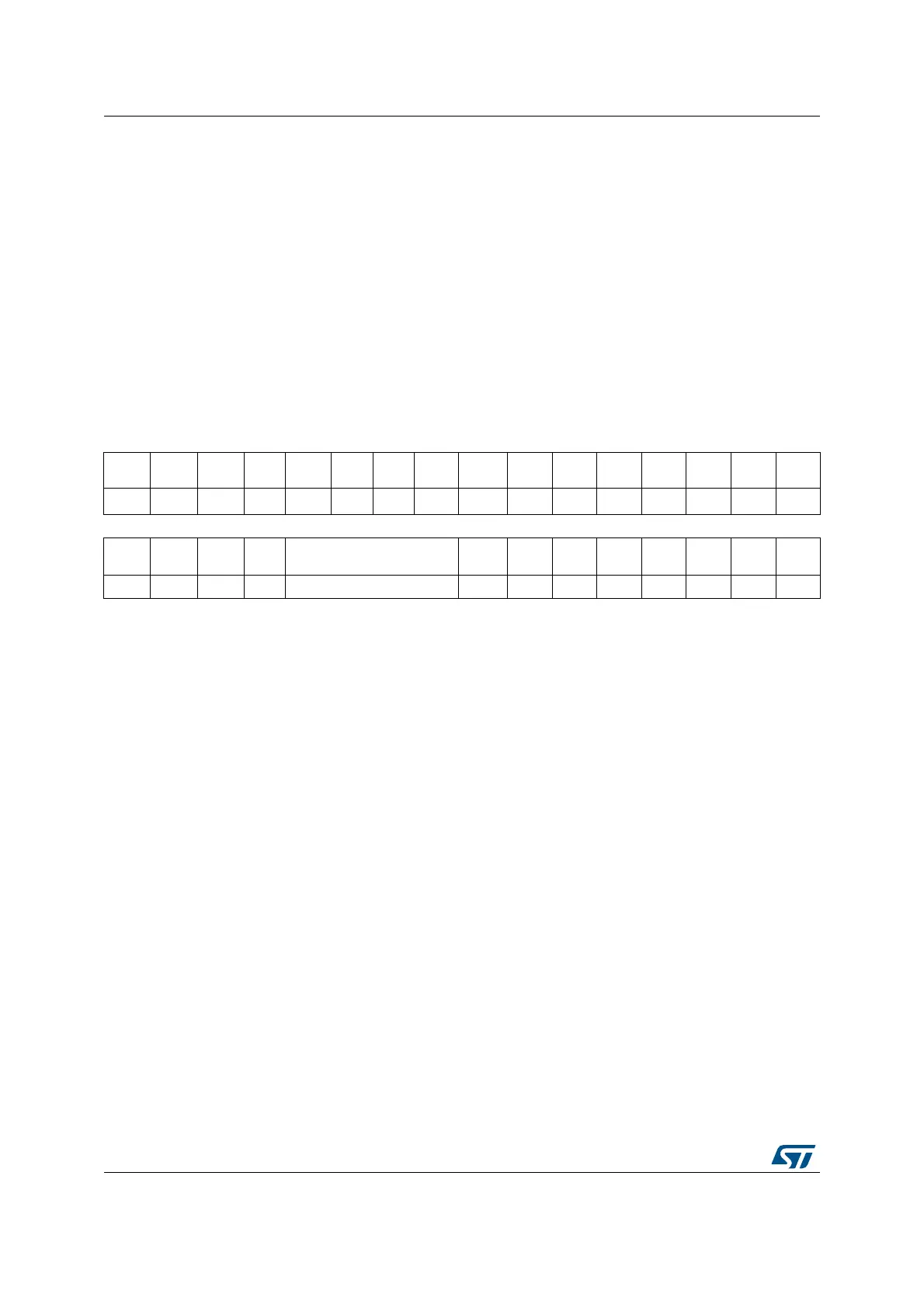

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. PECEN

ALERT

EN

SMBD

EN

SMBH

EN

GCEN Res.

NOSTR

ETCH

SBC

rw rw rw rw rw rw rw

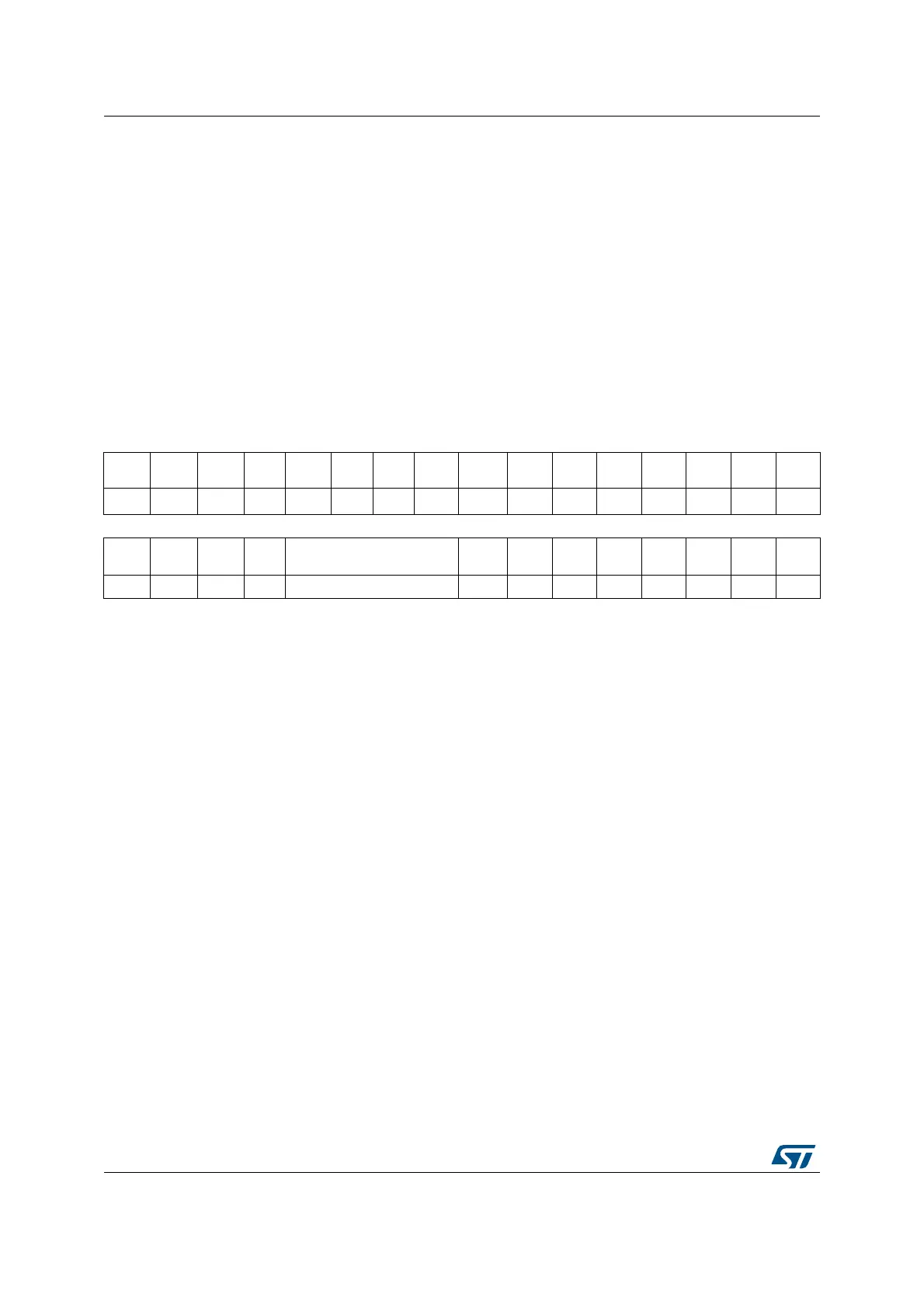

15141312111098 7 6543210

RXDMA

EN

TXDMA

EN

Res.

ANF

OFF

DNF ERRIE TCIE

STOP

IE

NACK

IE

ADDR

IE

RXIE TXIE PE

rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:24 Reserved, must be kept at reset value.

Bit 23 PECEN: PEC enable

0: PEC calculation disabled

1: PEC calculation enabled

Note: If the SMBus feature is not supported, this bit is reserved and forced by hardware to ‘0’.

Refer to Section 23.3: FMPI2C implementation.

Bit 22 ALERTEN: SMBus alert enable

Device mode (SMBHEN=0):

0: Releases SMBA pin high and Alert Response Address Header disabled: 0001100x

followed by NACK.

1: Drives SMBA pin low and Alert Response Address Header enables: 0001100x followed

by ACK.

Host mode (SMBHEN=1):

0: SMBus Alert pin (SMBA) not supported.

1: SMBus Alert pin (SMBA) supported.

Note: When ALERTEN=0, the SMBA pin can be used as a standard GPIO.

If the SMBus feature is not supported, this bit is reserved and forced by hardware to ‘0’.

Refer to Section 23.3: FMPI2C implementation.

Bit 21 SMBDEN: SMBus Device Default address enable

0: Device default address disabled. Address 0b1100001x is NACKed.

1: Device default address enabled. Address 0b1100001x is ACKed.

Note: If the SMBus feature is not supported, this bit is reserved and forced by hardware to ‘0’.

Refer to Section 23.3: FMPI2C implementation.

Loading...

Loading...