SPDIF receiver interface (SPDIFRX) RM0390

920/1328 RM0390 Rev 4

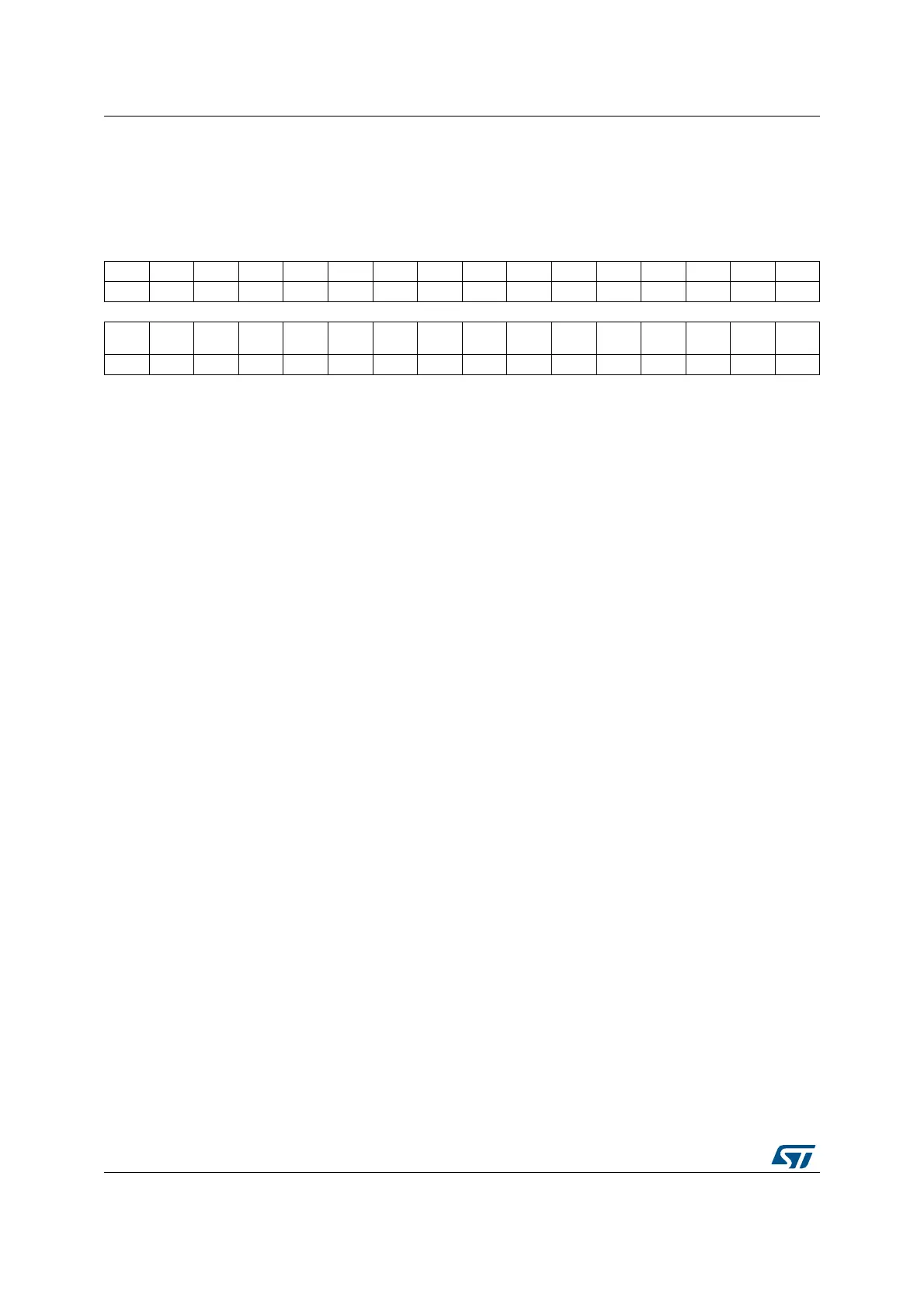

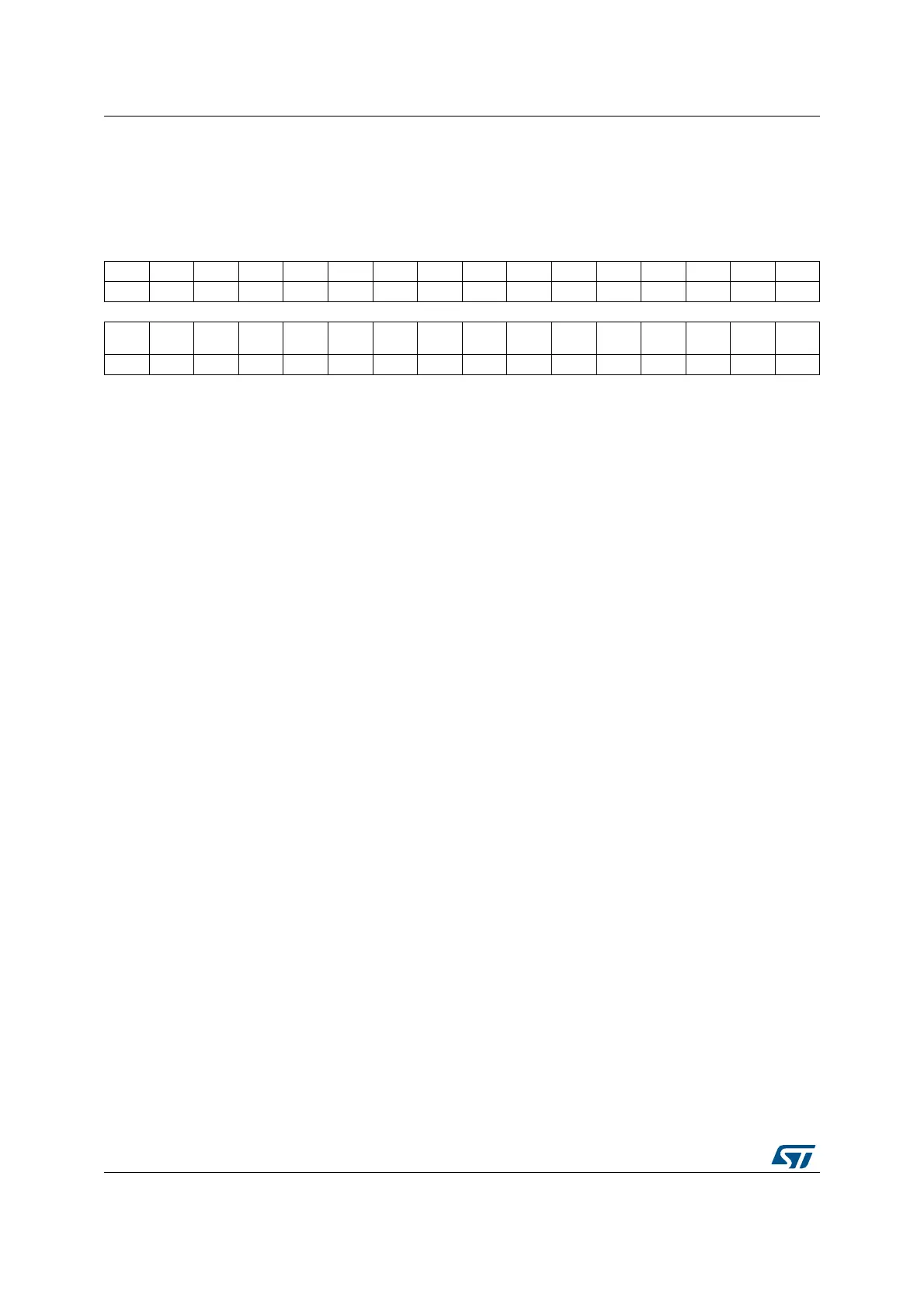

27.5.2 Interrupt mask register (SPDIFRX_IMR)

Address offset: 0x04

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res.

IFE

IE

SYNCD

IE

SBLK

IE

OVR

IE

PERR

IE

CSRNE

IE

RXNE

IE

rw rw rw rw rw rw rw

Bits 31:7 Reserved, must be kept at reset value.

Bit 6 IFEIE: Serial Interface Error Interrupt Enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever SERR=1, TERR=1 or FERR=1 in the

SPDIFRX_SR register.

Bit 5 SYNCDIE: Synchronization Done

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever SYNCD = 1 in the SPDIFRX_SR register.

Bit 4 SBLKIE: Synchronization Block Detected Interrupt Enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever SBD = 1 in the SPDIFRX_SR register.

Bit 3 OVRIE: Overrun error Interrupt Enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever OVR=1 in the SPDIFRX_SR register

Bit 2 PERRIE: Parity error interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever PERR=1 in the SPDIFRX_SR register

Bit 1 CSRNEIE: Control Buffer Ready Interrupt Enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever CSRNE = 1 in the SPDIFRX_SR register.

Bit 0 RXNEIE: RXNE interrupt enable

This bit is set and cleared by software.

0: Interrupt is inhibited

1: A SPDIFRX interface interrupt is generated whenever RXNE=1 in the SPDIFRX_SR register

Loading...

Loading...