SPDIF receiver interface (SPDIFRX) RM0390

914/1328 RM0390 Rev 4

SPDIFRX interface sends a transfer request to the DMA. The DMA reads the data received

through the SPDIFRX_DR register without CPU intervention.

For the use of DMA for the control data refer to Section 27.3.7: Dedicated control flow.

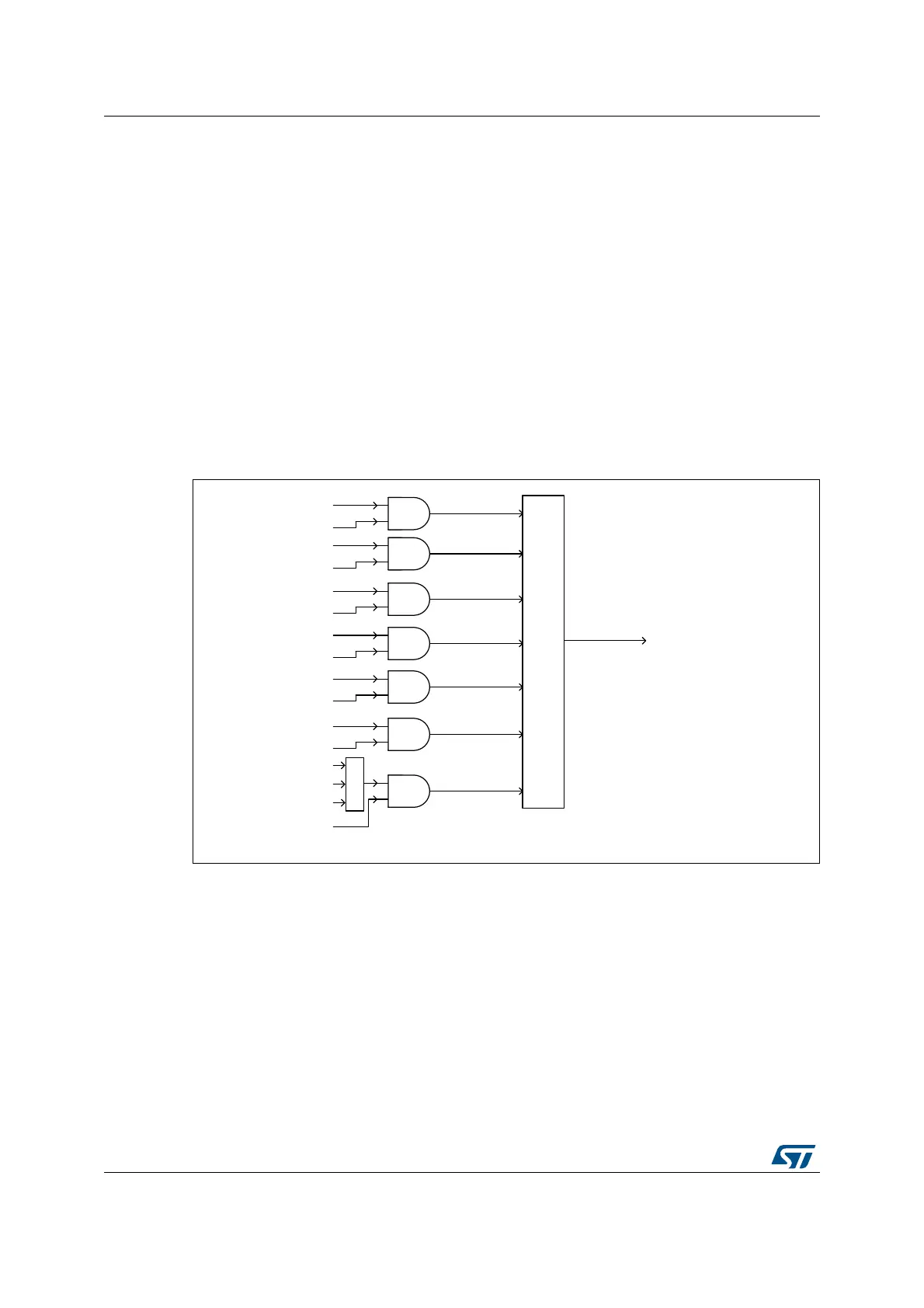

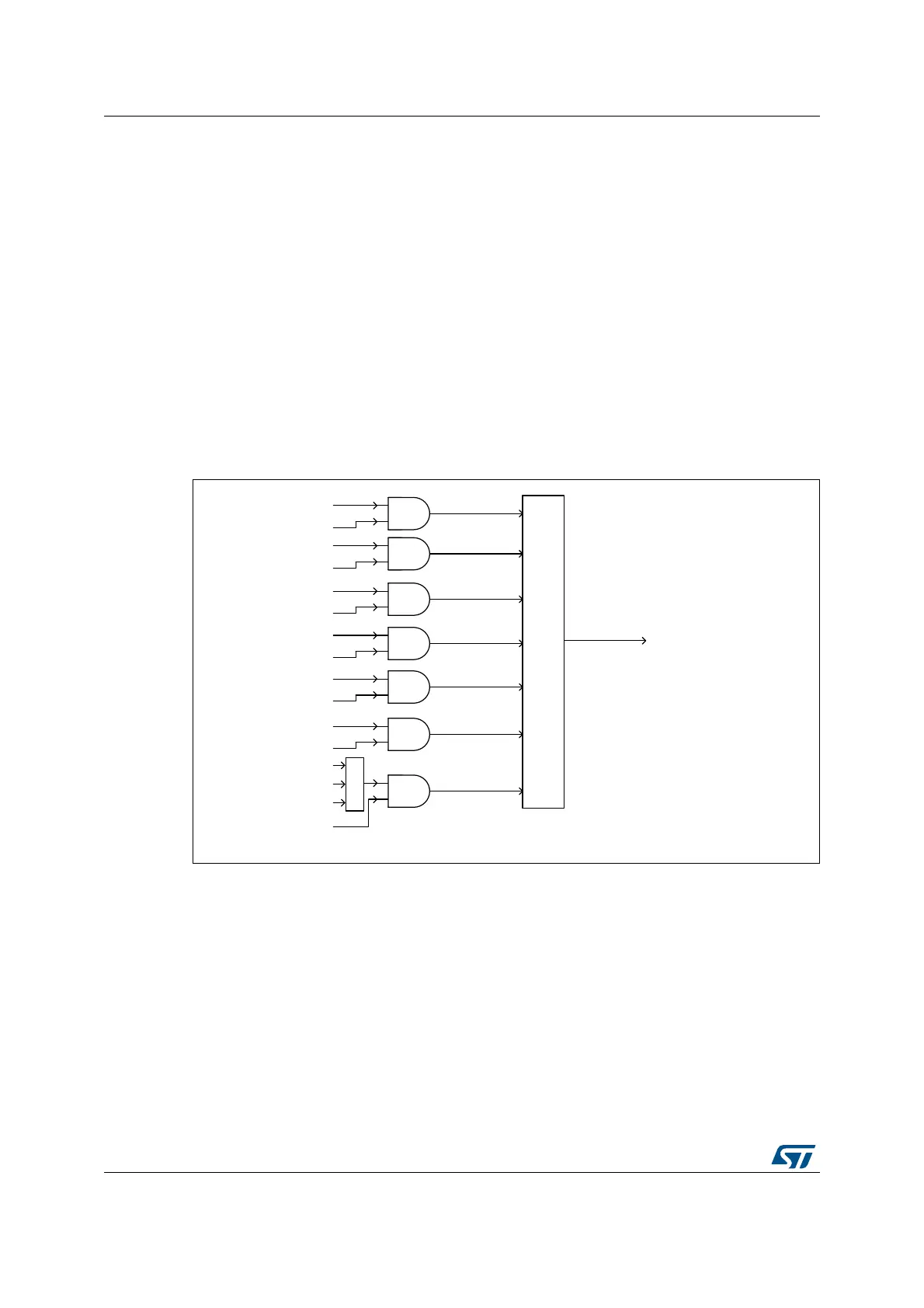

27.3.11 Interrupt Generation

An interrupt line is shared between:

• Reception events for data flow (RXNE)

• Reception event for control flow (CSRNE)

• Data corruption detection (PERR)

• Transfer flow interruption (OVR)

• Frame structure and synchronization errors (SERR, TERR and FERR)

• Start of new block interrupt (SBD)

• Synchronization done (SYNCD)

Figure 353. SPDIFRX interface interrupt mapping diagram

Clearing interrupt source

• RXNE is cleared when SPDIFRX_DR register is read

• CSRNE is cleared when SPDIFRX_CSR register is read

• FERR is cleared when SPDIFRXEN is set to 0

• SERR is cleared when SPDIFRXEN is set to 0

• TERR is cleared when SPDIFRXEN is set to 0

• Others are cleared through SPDIFRX_IFCR register

Note: The SBD event can only occur when the SPDIFRX is synchronized to the input stream

(SYNCD = 1).

25

5;1(

5;1(,(

3(55

3(55,(

295

295,(

25

&651(

&651(,(

6%'

6%',(

6(55

)(55

,)(,(

63',)5;B,54

7(55

6<1&'

6<1&',(

06Y9

Loading...

Loading...