SPDIF receiver interface (SPDIFRX) RM0390

924/1328 RM0390 Rev 4

27.5.5 Data input register (SPDIFRX_DR)

Address offset: 0x10

Reset value: 0x0000 0000

This register can take 3 different formats according to DRFMT. Here is the format when

DRFMT = 0b00:

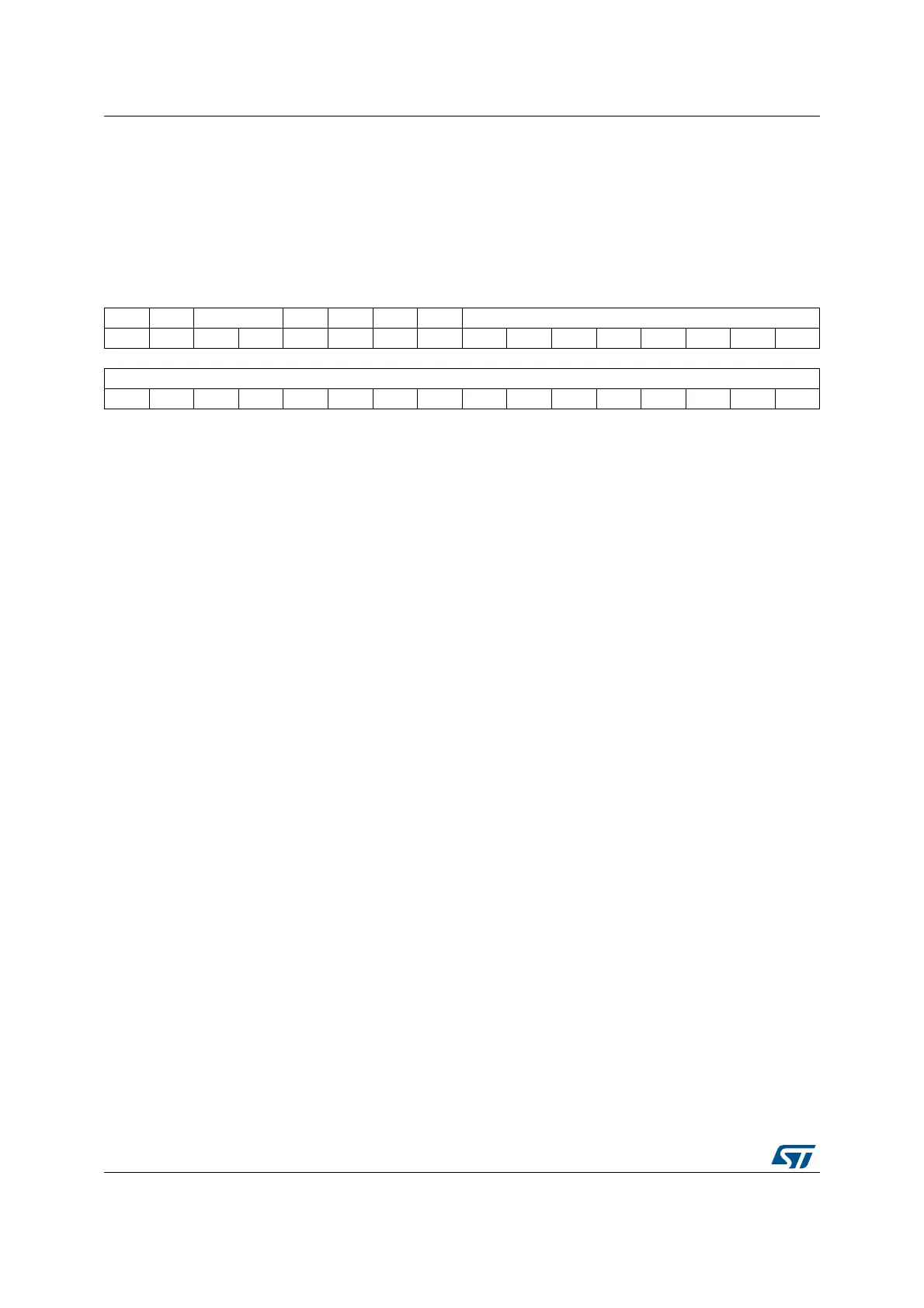

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. PT[1:0] C U V PE DR[23:16]

rrrrrrrrrrrrrr

1514131211109876543210

DR[15:0]

rrrrrrrrrrrrrrrr

Bits 31:30 Reserved, must be kept at reset value.

Bits 29:28 PT[1:0]: Preamble Type

These bits indicate the preamble received.

00: not used

01: Preamble B received

10: Preamble M received

11: Preamble W received

Note that if PTMSK = 1, this field is forced to zero

Bit 27 C: Channel Status bit

Contains the received channel status bit, if CUMSK = 0, otherwise it is forced to 0

Bit 26 U: User bit

Contains the received user bit, if CUMSK = 0, otherwise it is forced to 0

Bit 25 V: Validity bit

Contains the received validity bit if VMSK = 0, otherwise it is forced to 0

Bit 24 PE: Parity Error bit

Contains a copy of PERR bit if PMSK = 0, otherwise it is forced to 0

Bits 23:0 DR[23:0]: Data value

Contains the 24 received data bits, aligned on D[23]

Loading...

Loading...