RM0390 Rev 4 1097/1328

RM0390 USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS)

1264

The end of periodic frame interrupt (OTG_GINTSTS/EOPF) is used to notify the application

when 80%, 85%, 90% or 95% of the time frame interval elapsed depending on the periodic

frame interval field in the device configuration register (PFIVL bit in OTG_DCFG). This

feature can be used to determine if all of the isochronous traffic for that frame is complete.

31.9 OTG low-power modes

Table 222 below defines the STM32 low power modes and their compatibility with the OTG.

The following bits and procedures reduce power consumption.

The power consumption of the OTG PHY is controlled by two or three bits in the general

core configuration register, depending on OTG revision supported.

• PHY power down (OTG_GCCFG/PWRDWN)

It switches on/off the full-speed transceiver module of the PHY. It must be preliminarily

set to allow any USB operation

• V

BUS

detection enable (OTG_GCCFG/VBDEN)

It switches on/off the V

BUS

sensing comparators associated with OTG operations

Power reduction techniques are available while in the USB suspended state, when the USB

session is not yet valid or the device is disconnected.

• Stop PHY clock (STPPCLK bit in OTG_PCGCCTL)

When setting the stop PHY clock bit in the clock gating control register, most of the

48 MHz clock domain internal to the OTG full-speed core is switched off by clock

gating. The dynamic power consumption due to the USB clock switching activity is cut

even if the 48 MHz clock input is kept running by the application

Most of the transceiver is also disabled, and only the part in charge of detecting the

asynchronous resume or remote wakeup event is kept alive.

• Gate HCLK (GATEHCLK bit in OTG_PCGCCTL)

When setting the Gate HCLK bit in the clock gating control register, most of the system

clock domain internal to the OTG_FS/OTG_HS core is switched off by clock gating.

Only the register read and write interface is kept alive. The dynamic power

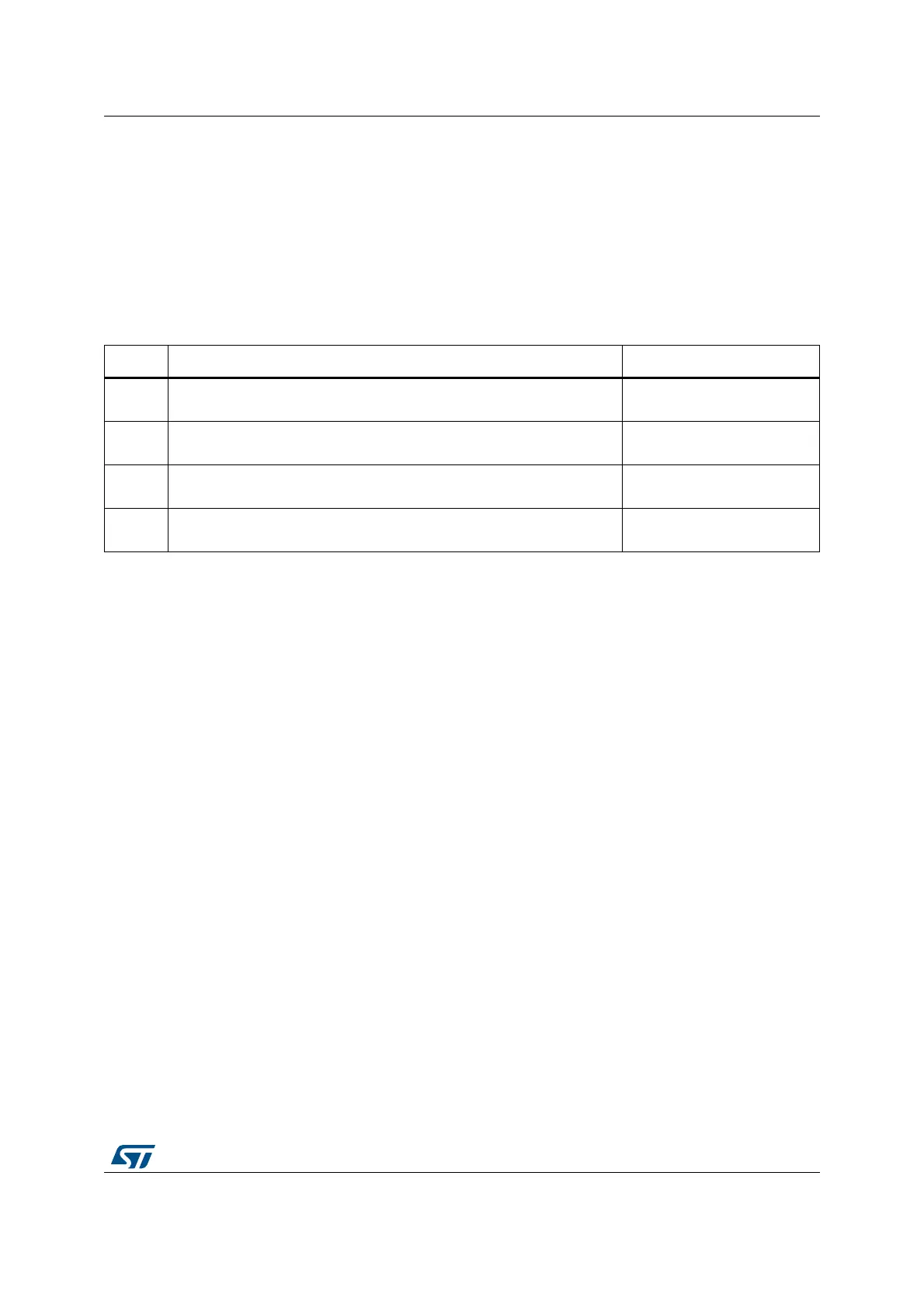

Table 222. Compatibility of STM32 low power modes with the OTG

Mode Description USB compatibility

Run MCU fully active

Required when USB not in

suspend state.

Sleep

USB suspend exit causes the device to exit Sleep mode. Peripheral

registers content is kept.

Available while USB is in

suspend state.

Stop

USB suspend exit causes the device to exit Stop mode. Peripheral

registers content is kept

(1)

.

Available while USB is in

suspend state.

Standby

Powered-down. The peripheral must be reinitialized after exiting

Standby mode.

Not compatible with USB

applications.

1. Within Stop mode there are different possible settings. Some restrictions may also exist, please refer to Section 5: Power

controller (PWR) to understand which (if any) restrictions apply when using OTG.

Loading...

Loading...