SPDIF receiver interface (SPDIFRX) RM0390

926/1328 RM0390 Rev 4

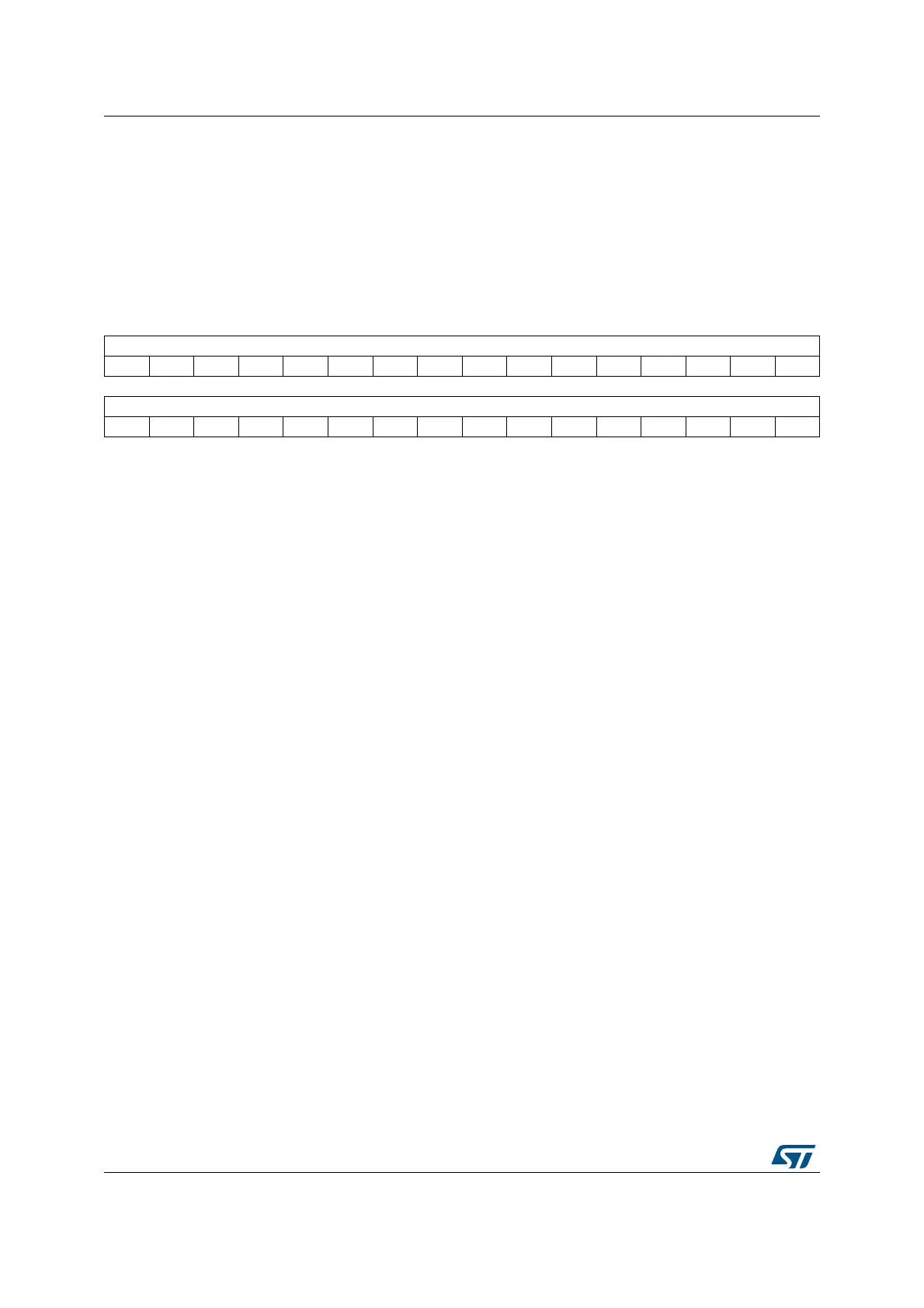

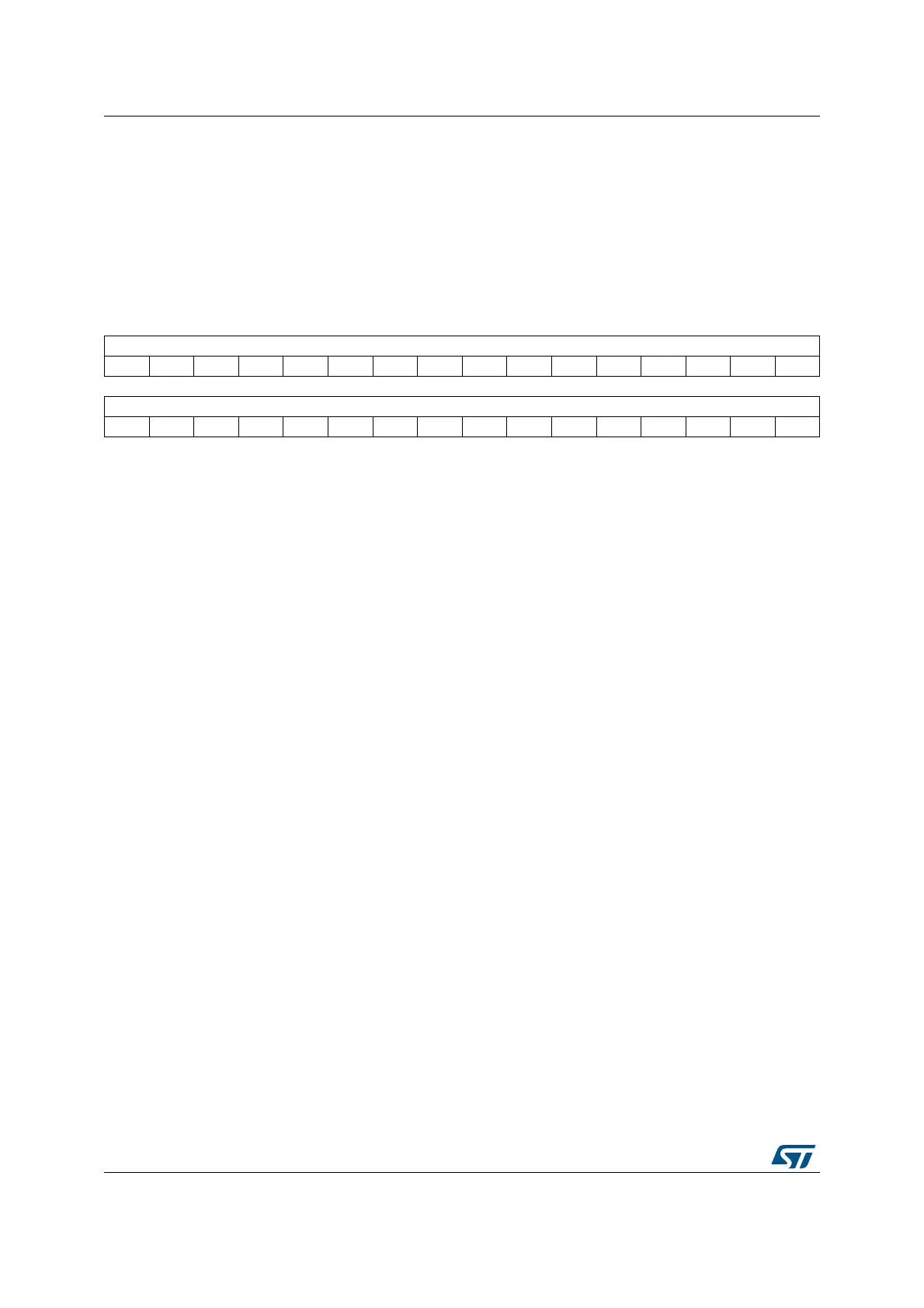

27.5.7 Data input register (SPDIFRX_FMT2_DR)

Address offset: 0x10

Reset value: 0x0000 0000

This register can take 3 different formats according to DRFMT.

The data format proposed when DRFMT = 0b10, is dedicated to non-linear mode, as only

16 bits are used (bits 23 to 8 from S/PDIF sub-frame).

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

DRNL2[15:0]

rrrrrrrrrrrrrrrr

1514131211109876543210

DRNL1[15:0]

rrrrrrrrrrrrrrrr

Bits 31:16 DRNL2[15:0]: Data value

This field contains the Channel A

Bits 15:0 DRNL1[15:0]: Data value

This field contains the Channel B

Loading...

Loading...