RM0390 Rev 4 1249/1328

RM0390 USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS)

1264

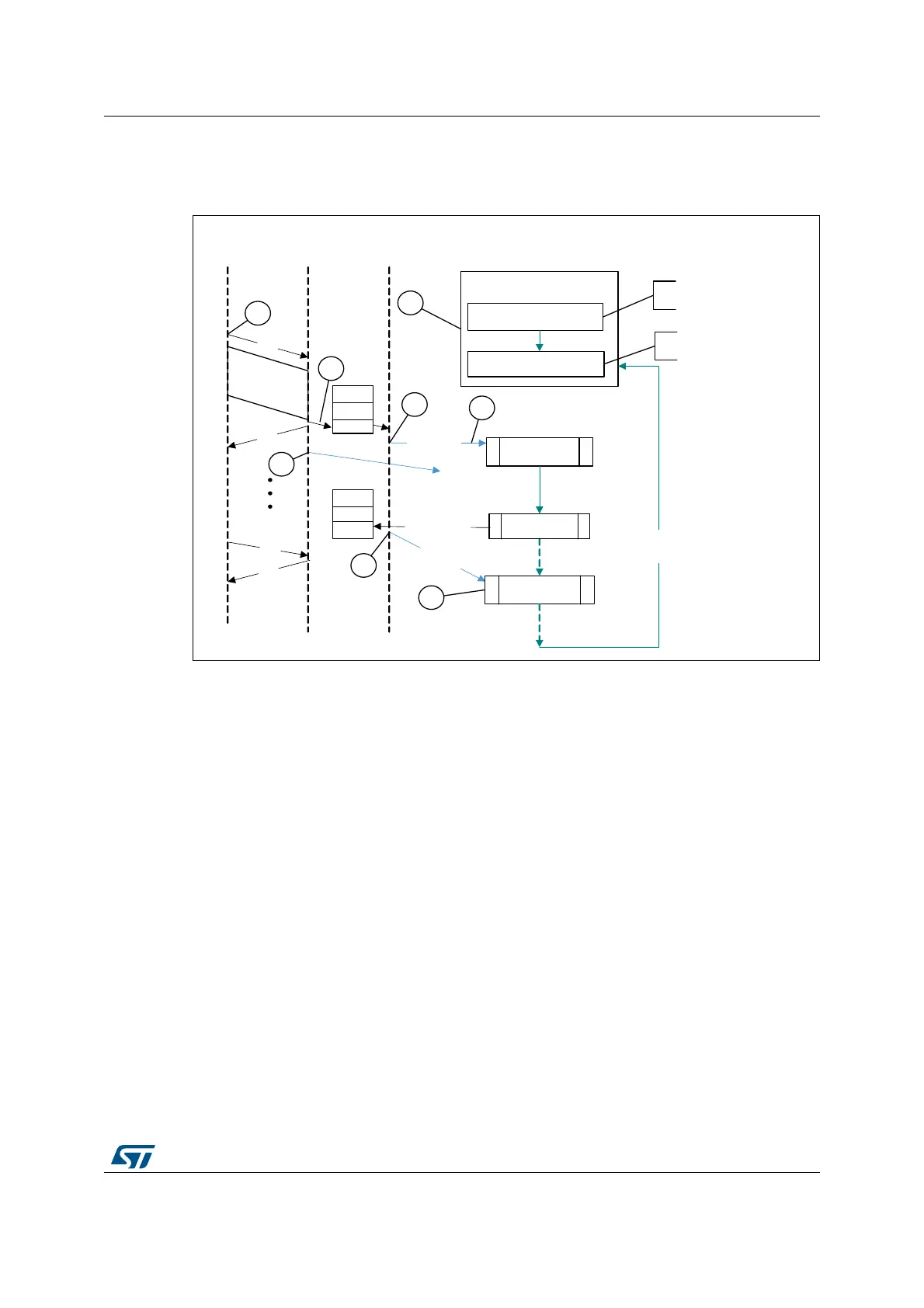

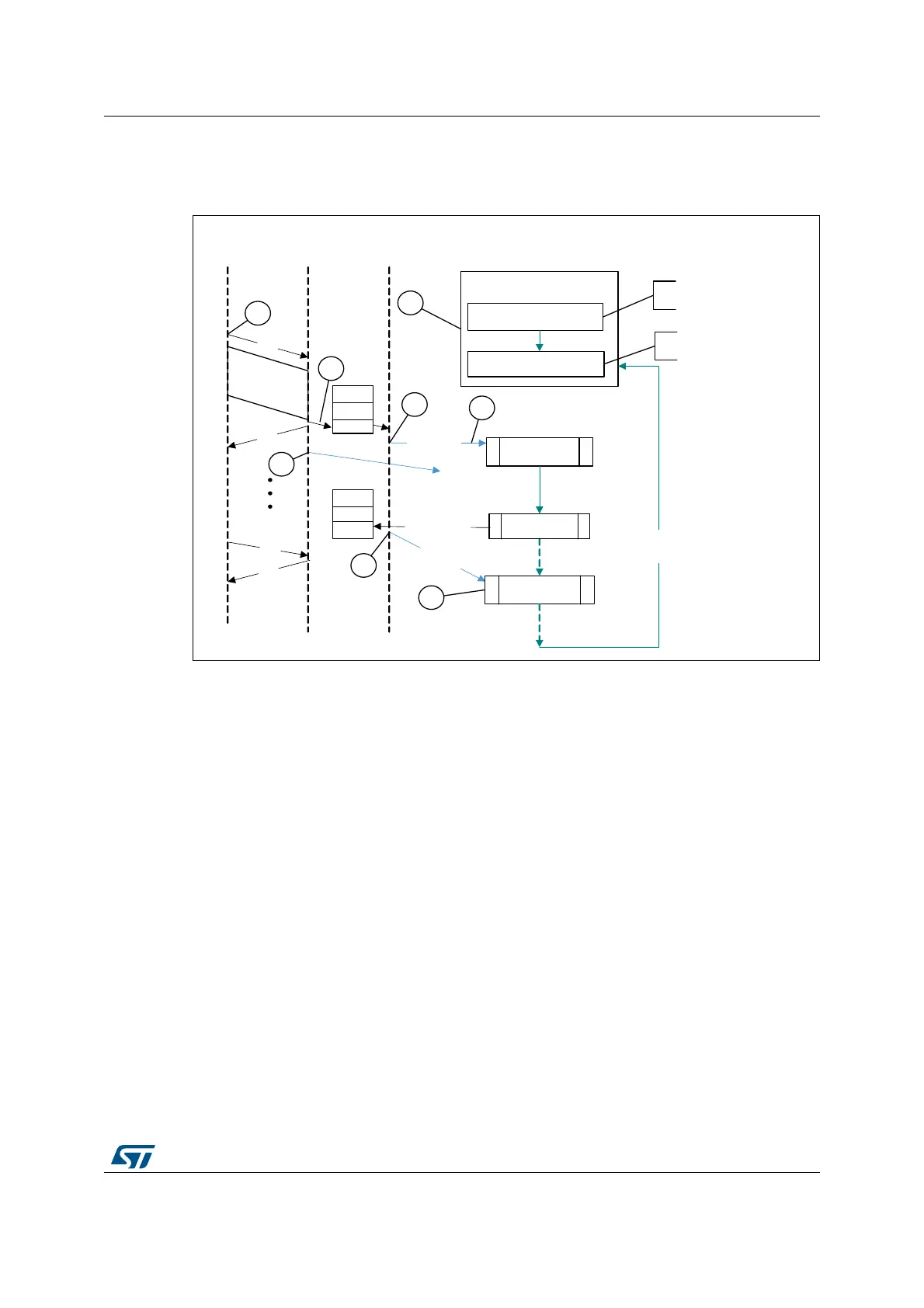

Figure 426 depicts the reception of a single Bulk OUT data packet from the USB to the AHB

and describes the events involved in the process.

Figure 426. Bulk OUT transaction

After a SetConfiguration/SetInterface command, the application initializes all OUT endpoints

by setting CNAK = 1 and EPENA = 1 (in OTG_DOEPCTLx), and setting a suitable

XFRSIZ and PKTCNT in the OTG_DOEPTSIZx register.

1. host attempts to send data (OUT token) to an endpoint.

2. When the core receives the OUT token on the USB, it stores the packet in the Rx FIFO

because space is available there.

3. After writing the complete packet in the Rx FIFO, the core then asserts the RXFLVL

interrupt (in OTG_GINTSTS).

4. On receiving the PKTCNT number of USB packets, the core internally sets the NAK bit

for this endpoint to prevent it from receiving any more packets.

5. The application processes the interrupt and reads the data from the Rx FIFO.

6. When the application has read all the data (equivalent to XFRSIZ), the core generates

an XFRC interrupt (in OTG_DOEPINTx).

7. The application processes the interrupt and uses the setting of the XFRC interrupt bit

(in OTG_DOEPINTx) to determine that the intended transfer is complete.

IN data transfers

• Packet write

This section describes how the application writes data packets to the endpoint FIFO when

dedicated transmit FIFOs are enabled.

069

LQLW BRXWB HS

2

8

7

$

&

.

5;)/9/ LQWUL

:UBUHJ27*B'2(376,=[

:UBUHJ27*B'2(3&7/[

E\WHV

2

8

7

1

$

.

[DFWB

;)5&

L

Q

W

U

;)56,=

U

LGOH XQWLO LQWU

UFYBRXWBSNW

LGOH XQWLO LQWU

2Q QHZ [IHU

RU 5[),)2

QRWHP SW\

;)56,=

E\WHV

3.7&17

(3(1$

&1$.

+RVW 86% 'HYLFH $SSOLFDWLRQ

3.7&17

27*B'2(3&7/[1$.

Loading...

Loading...