Secure digital input/output interface (SDIO) RM0390

1026/1328 RM0390 Rev 4

29.8.13 SDIO mask register (SDIO_MASK)

Address offset: 0x3C

Reset value: 0x0000 0000

The interrupt mask register determines which status flags generate an interrupt request by

setting the corresponding bit to 1b.

Bit 2 CTIMEOUTC: CTIMEOUT flag clear bit

Set by software to clear the CTIMEOUT flag.

0: CTIMEOUT not cleared

1: CTIMEOUT cleared

Bit 1 DCRCFAILC: DCRCFAIL flag clear bit

Set by software to clear the DCRCFAIL flag.

0: DCRCFAIL not cleared

1: DCRCFAIL cleared

Bit 0 CCRCFAILC: CCRCFAIL flag clear bit

Set by software to clear the CCRCFAIL flag.

0: CCRCFAIL not cleared

1: CCRCFAIL cleared

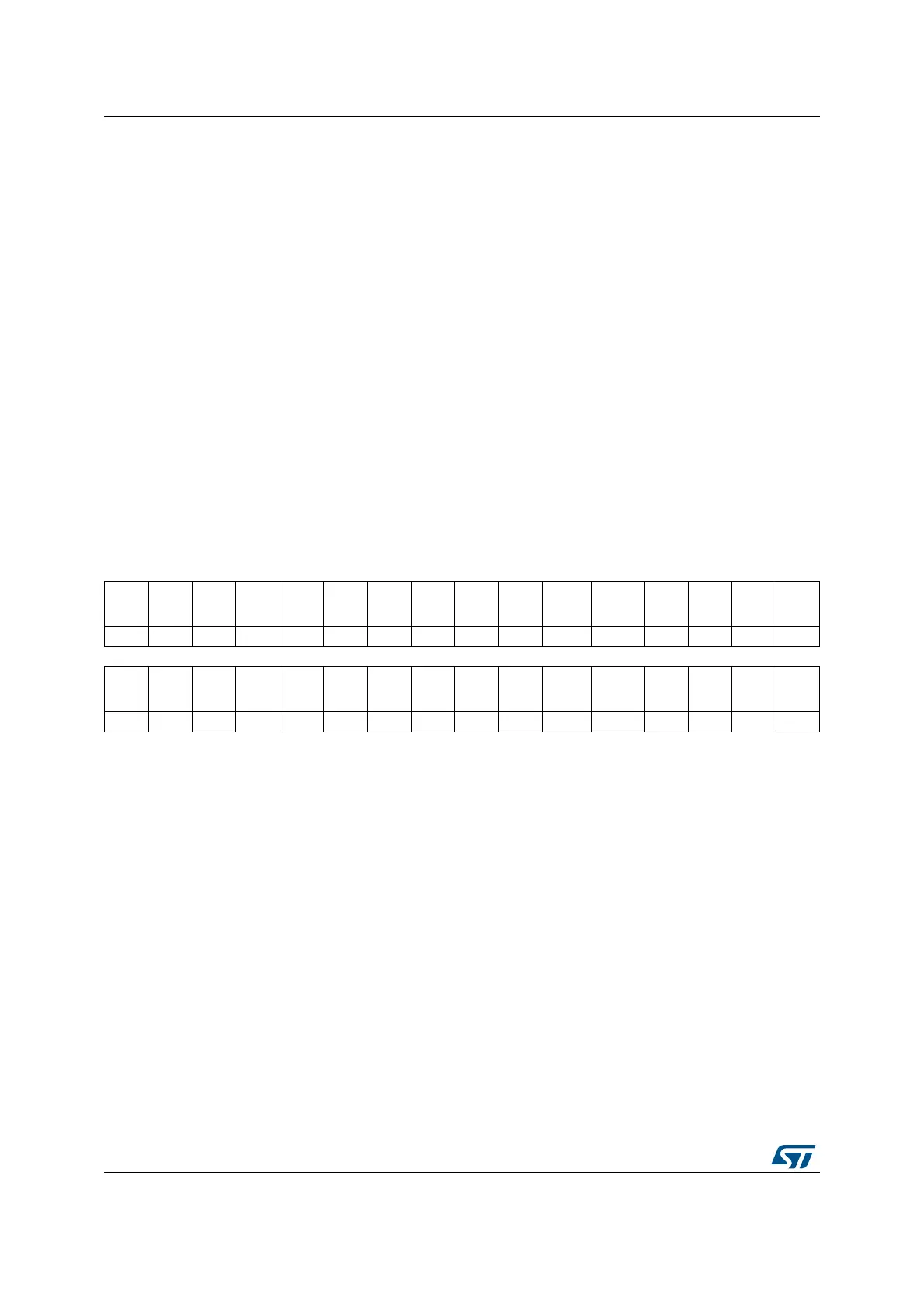

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res.

SDIO

ITIE

RXD

AVLIE

TXD

AVLIE

RX

FIFO

EIE

TX

FIFO

EIE

RX

FIFO

FIE

TX

FIFO

FIE

rw rw rw rw rw rw rw

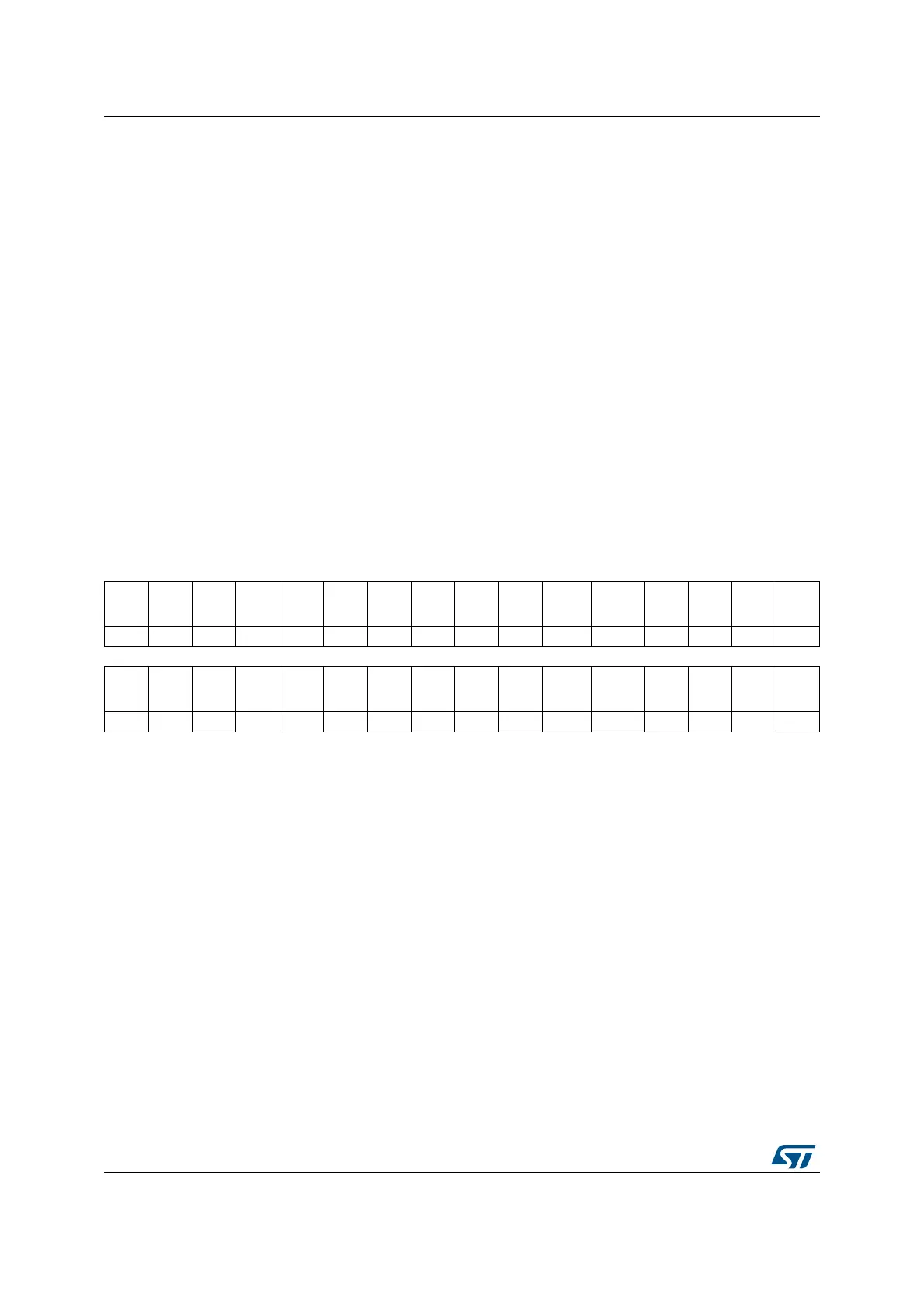

1514131211109876 5 4 3210

RX

FIFO

HFIE

TX

FIFO

HEIE

RX

ACTIE

TX

ACTIE

CMD

ACTIE

DBCK

ENDIE

Res.

DATA

ENDIE

CMD

SENT

IE

CMD

REND

IE

RX

OVERR

IE

TX

UNDERR

IE

DTIME

OUTIE

CTIME

OUTIE

DCRC

FAILIE

CCRC

FAILIE

rw rw rw rw rw rw rw rw rw rw rw rw rw rw rw

Bits 31:23 Reserved, must be kept at reset value.

Bit 22 SDIOITIE: SDIO mode interrupt received interrupt enable

Set and cleared by software to enable/disable the interrupt generated when receiving the

SDIO mode interrupt.

0: SDIO Mode Interrupt Received interrupt disabled

1: SDIO Mode Interrupt Received interrupt enabled

Bit 21 RXDAVLIE: Data available in Rx FIFO interrupt enable

Set and cleared by software to enable/disable the interrupt generated by the presence of

data available in Rx FIFO.

0: Data available in Rx FIFO interrupt disabled

1: Data available in Rx FIFO interrupt enabled

Bit 20 TXDAVLIE: Data available in Tx FIFO interrupt enable

Set and cleared by software to enable/disable the interrupt generated by the presence of

data available in Tx FIFO.

0: Data available in Tx FIFO interrupt disabled

1: Data available in Tx FIFO interrupt enabled

Loading...

Loading...