Serial audio interface (SAI) RM0390

962/1328 RM0390 Rev 4

28.5.3 Configuration register 2 (SAI_ACR2 / SAI_BCR2)

Address offset: Block A: 0x008

Address offset: Block B: 0x028

Reset value: 0x0000 0000

Bit 4 Reserved, must be kept at reset value.

Bits 3:2 PRTCFG[1:0]: Protocol configuration

These bits are set and cleared by software. These bits have to be configured when the audio block is

disabled.

00: Free protocol. Free protocol allows to use the powerful configuration of the audio block to

address a specific audio protocol (such as I2S, LSB/MSB justified, TDM, PCM/DSP...) by setting

most of the configuration register bits as well as frame configuration register.

01: SPDIF protocol

10: AC’97 protocol

11: Reserved

Bits 1:0 MODE[1:0]: SAIx audio block mode

These bits are set and cleared by software. They must be configured when SAIx audio block is

disabled.

00: Master transmitter

01: Master receiver

10: Slave transmitter

11: Slave receiver

Note: When the audio block is configured in SPDIF mode, the master transmitter mode is forced

(MODE[1:0] = 00). In Master transmitter mode, the audio block starts generating the FS and the

clocks immediately.

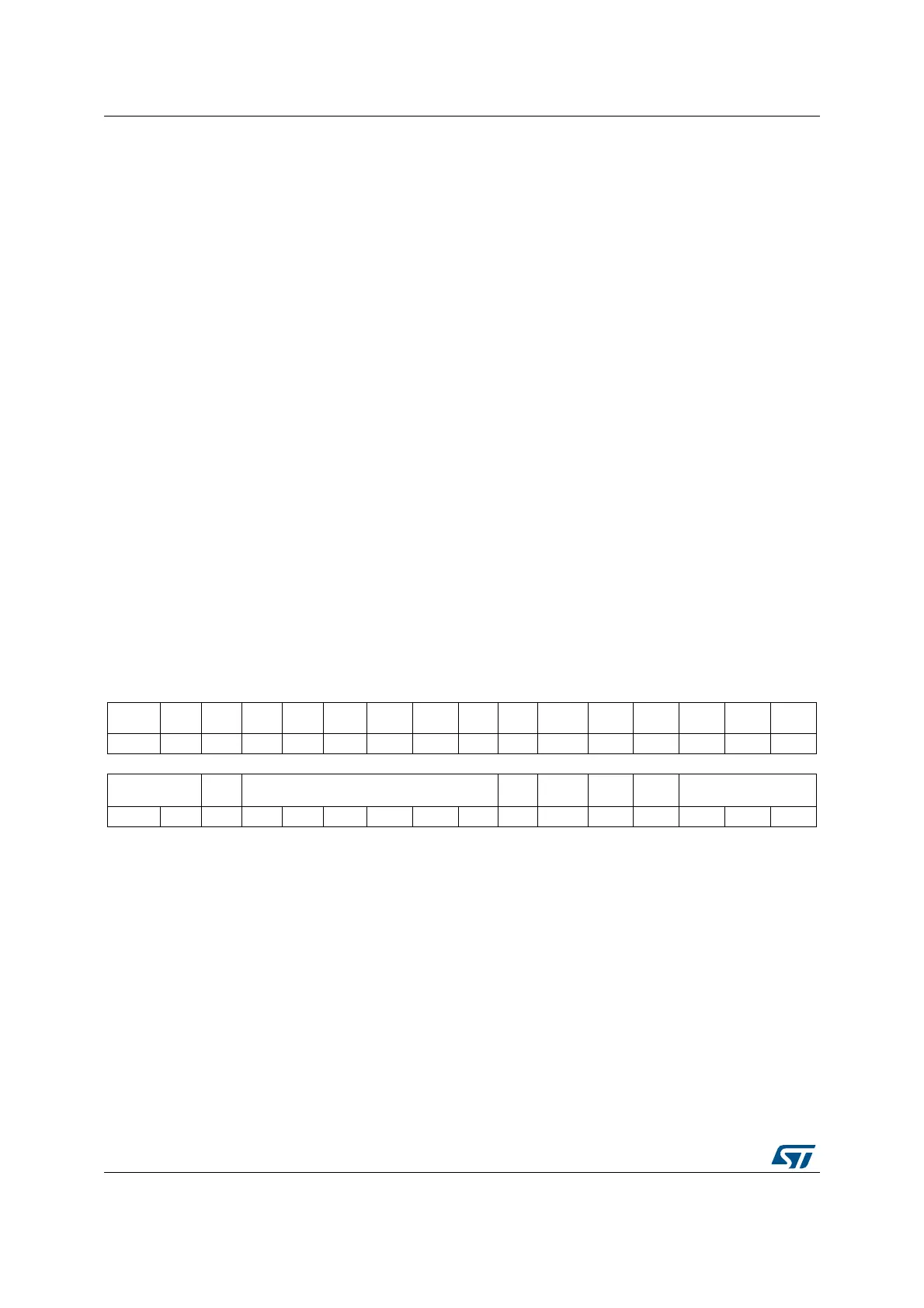

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

COMP[1:0] CPL MUTECNT[5:0]

MUTE

VAL

MUTE TRIS

F

FLUSH

FTH[2:0]

rw rw rw rw rw rw rw rw rw rw rw rw w rw rw rw

Loading...

Loading...