RM0390 Rev 4 915/1328

RM0390 SPDIF receiver interface (SPDIFRX)

929

The SBD flag behavior is not guaranteed when the sub-frame which contains the B

preamble is lost due to an overrun.

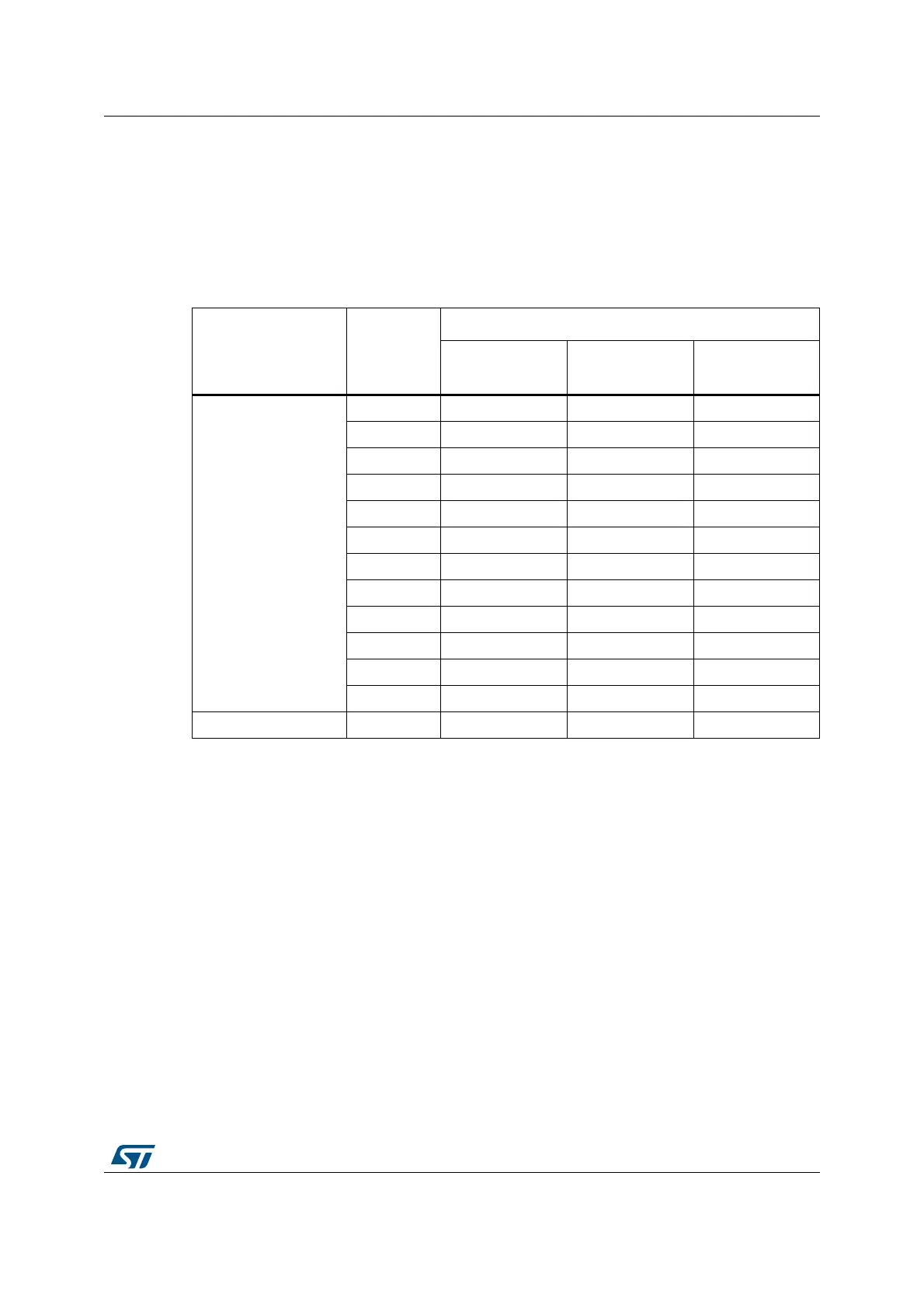

27.3.12 Register protection

The SPDIFRX block embeds some hardware protection avoid erroneous use of control

registers. The table hereafter shows the bit field properties according to the SPDIFRX state.

The table clearly shows that fields such as INSEL must be programmed when the IP is in

STATE_IDLE. In the others IP states, the hardware prevents writing to this field.

Note: Even if the hardware allows the writing of CBDMAEN and RXDMAEN “on-the-fly”, it is not

recommended to enable the DMA when the IP is already receiving data.

Note: Note that each of the mask bits (PMSK, VMSK, …) can be changed “on-the-fly” at any IP

state, but any change does not affect data which is already being held in SPDIFRX_DR.

27.4 Programming procedures

The following example illustrates a complete activation sequence of the SPDIFRX block.

The data path and channel status & user information will both use a dedicated DMA

channel. The activation sequence is then split into the following steps:

• Wait for valid data on the selected SPDIFRX_IN input

• Synchronize to the S/PDIF stream

• Read the channel status and user information in order to setup the complete audio path

• Start data acquisition

Table 169. Bit field property versus SPDIFRX state

Registers Field

SPDIFRXEN

0b00

(STATE_IDLE)

0b01

(STATE_SYNC)

0b11

(STATE_RCV)

SPDIFRX_CR

INSEL rw r r

WFA rw r r

NBTR rw r r

CHSEL rw r r

CBDMAEN rw rw rw

PTMSK rw rw rw

CUMSK rw rw rw

VMSK rw rw rw

PMSK rw rw rw

DRFMT rw rw r

RXSTEO rw rw r

RXDMAEN rw rw rw

SPDIFRX_IMR All fields rw rw rw

Loading...

Loading...