RM0390 Rev 4 1275/1328

RM0390 HDMI-CEC controller (HDMI-CEC)

1283

32.7 HDMI-CEC registers

Refer to Section 1.1 on page 51 for a list of abbreviations used in register descriptions.

32.7.1 CEC control register (CEC_CR)

Address offset: 0x00

Reset value: 0x0000 0000

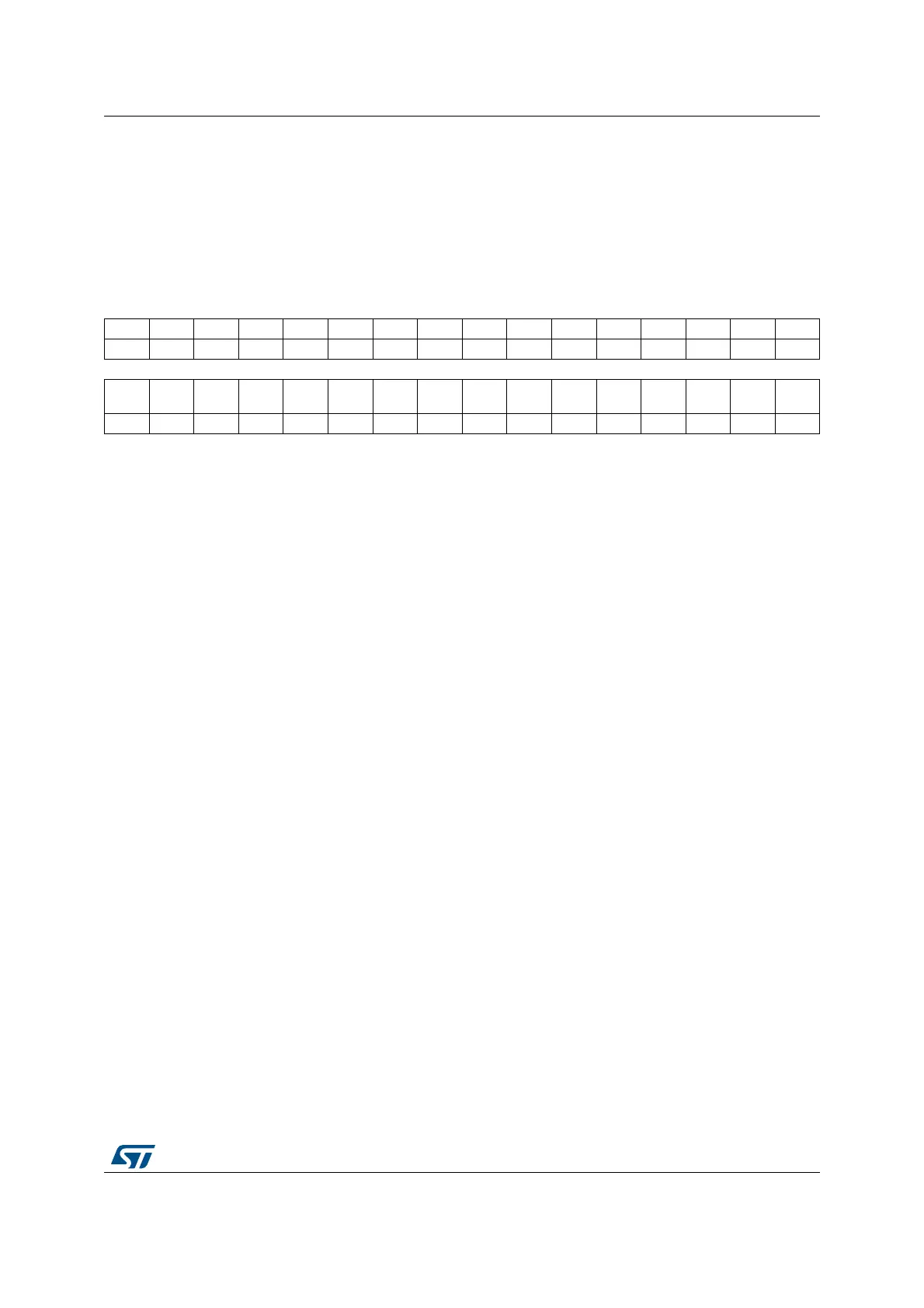

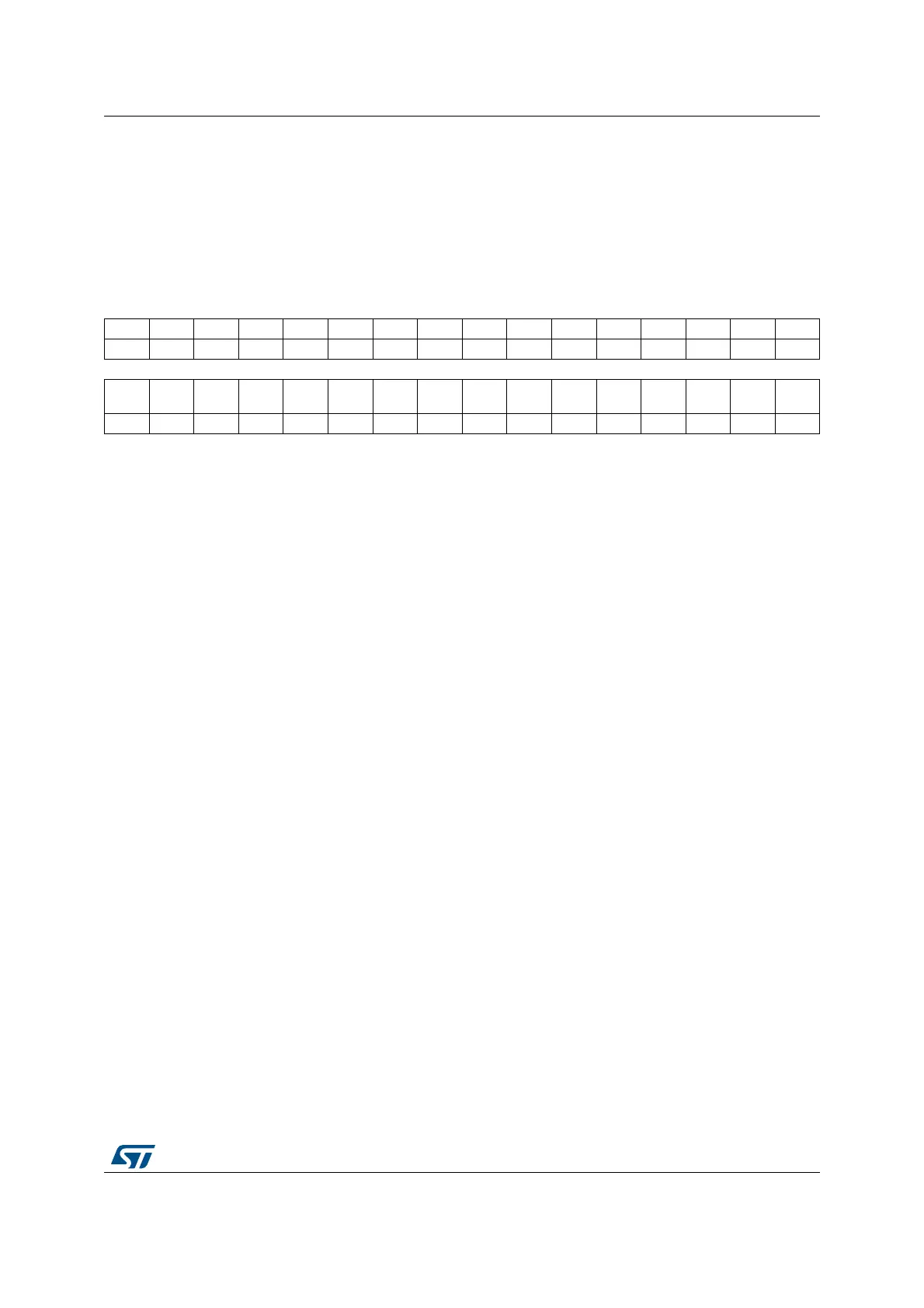

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

TX

EOM

TX

SOM

CEC

EN

rs rs rw

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 TXEOM: Tx End Of Message

The TXEOM bit is set by software to command transmission of the last byte of a CEC message.

TXEOM is cleared by hardware at the same time and under the same conditions as for TXSOM.

0: TXDR data byte is transmitted with EOM=0

1: TXDR data byte is transmitted with EOM=1

Note: TXEOM must be set when CECEN=1

TXEOM must be set before writing transmission data to TXDR

If TXEOM is set when TXSOM=0, transmitted message will consist of 1 byte (HEADER) only

(PING message)

Bit 1 TXSOM: Tx Start Of Message

TXSOM is set by software to command transmission of the first byte of a CEC message. If the CEC

message consists of only one byte, TXEOM must be set before of TXSOM.

Start-Bit is effectively started on the CEC line after SFT is counted. If TXSOM is set while a message

reception is ongoing, transmission will start after the end of reception.

TXSOM is cleared by hardware after the last byte of the message is sent with a positive acknowledge

(TXEND=1), in case of transmission underrun (TXUDR=1), negative acknowledge (TXACKE=1), and

transmission error (TXERR=1). It is also cleared by CECEN=0. It is not cleared and transmission is

automatically retried in case of arbitration lost (ARBLST=1).

Loading...

Loading...