RM0390 Rev 4 177/1328

RM0390 General-purpose I/Os (GPIO)

194

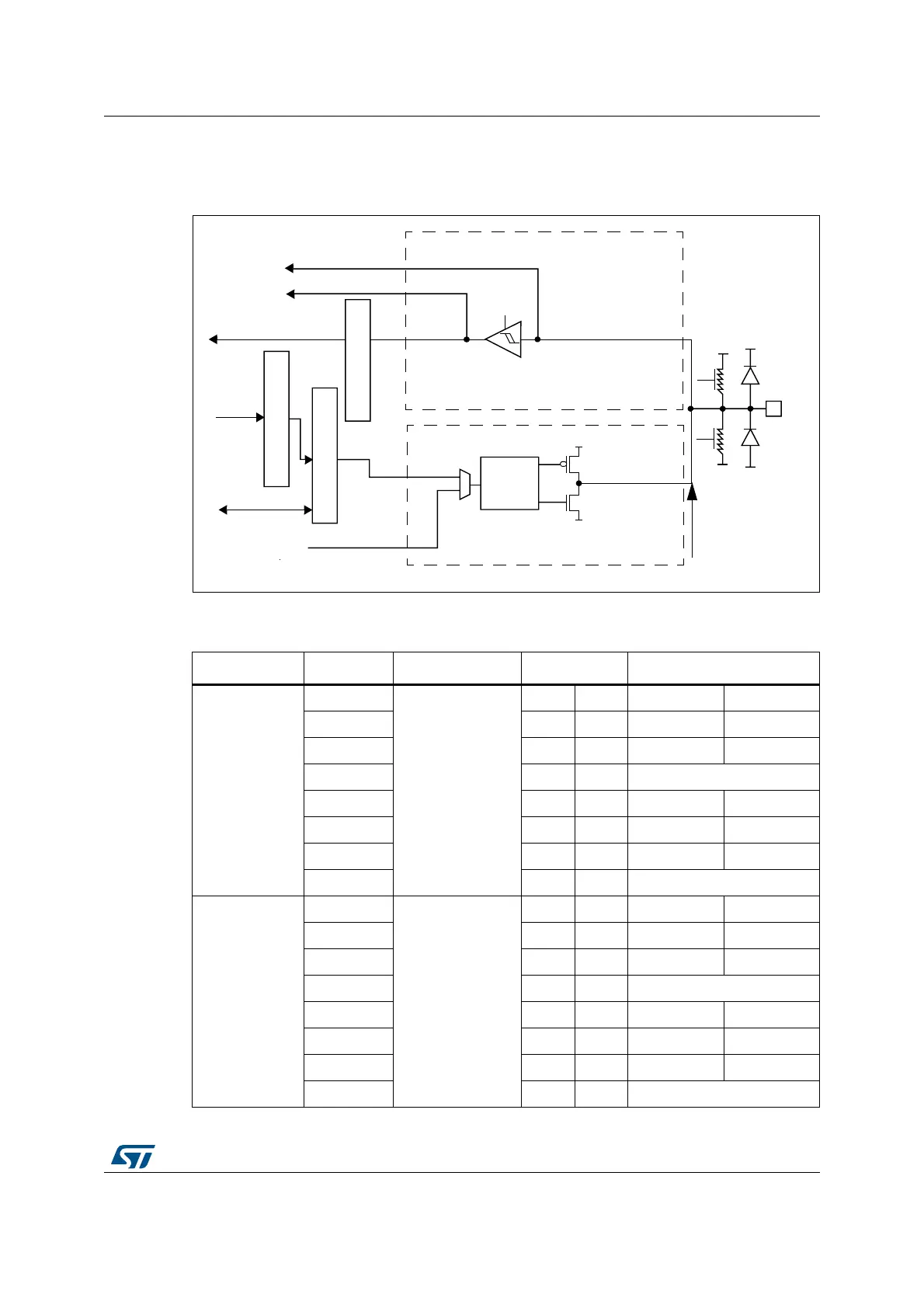

Figure 18 shows the basic structure of a 5 V tolerant I/O port bit, Table 22 gives the possible

port bit configurations.

Figure 18. Basic structure of a 5 V tolerant I/O port bit

1. V

DD_FT

is a potential specific to 5 V tolerant I/Os and different from V

DD

.

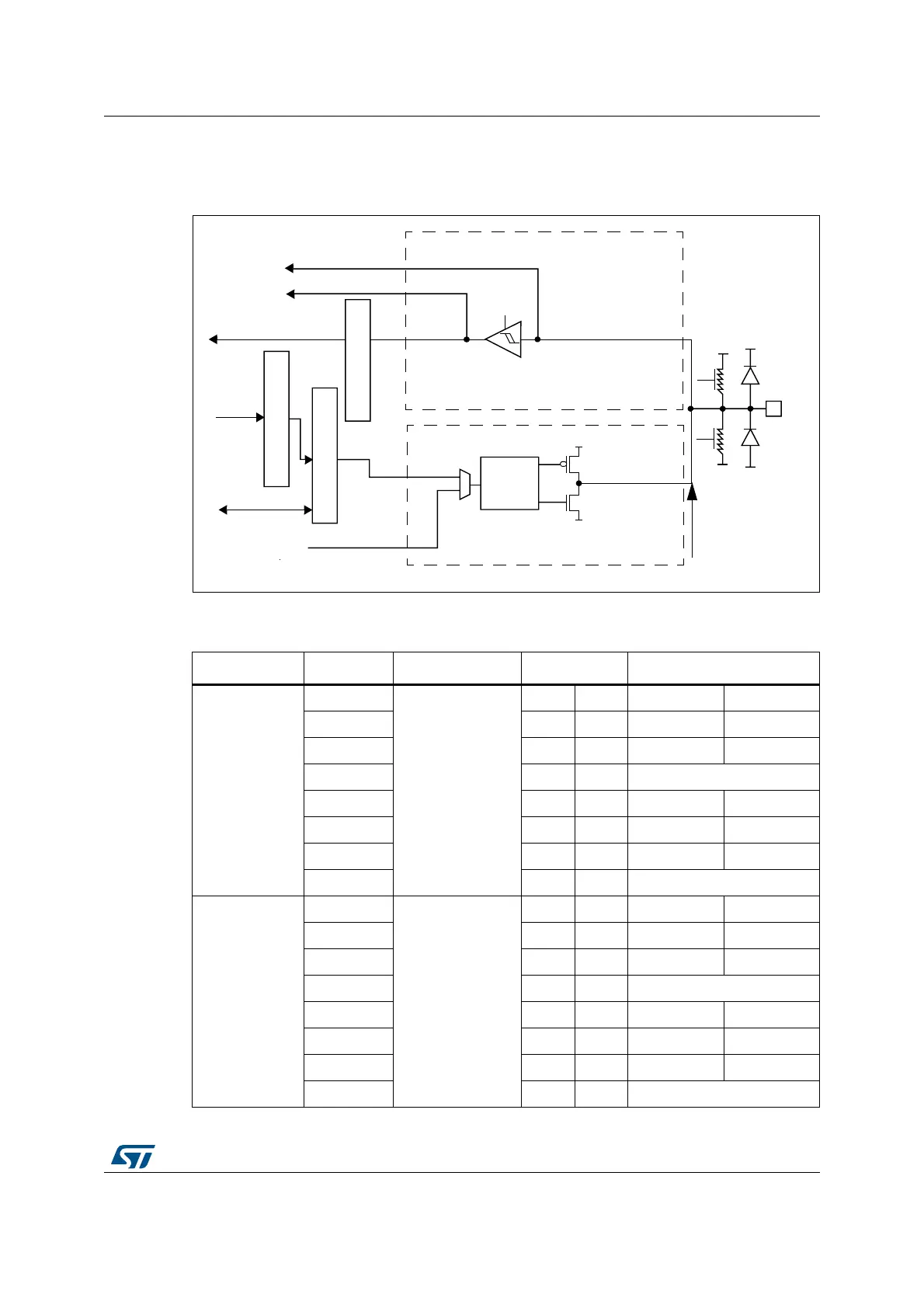

Table 22. Port bit configuration table

(1)

MODER(i)[1:0] OTYPER(i) OSPEEDR(i)[B:A] PUPDR(i)[1:0] I/O configuration

01

0

SPEED[B:A]

0 0 GP output PP

0 0 1 GP output PP + PU

0 1 0 GP output PP + PD

0 1 1 Reserved

1 0 0 GP output OD

1 0 1 GP output OD + PU

1 1 0 GP output OD + PD

1 1 1 Reserved (GP output OD)

10

0

SPEED[B:A]

0 0 AF PP

0 0 1 AF PP + PU

0 1 0 AF PP + PD

0 1 1 Reserved

100AFOD

101AFOD + PU

110AFOD + PD

1 1 1 Reserved

!LTERNATEFUNCTIONOUTPUT

!LTERNATEFUNCTIONINPUT

0USHPULL

OPENDRAINOR

DISABLED

/UTPUTDATAREGISTER

2EADWRITE

&ROMONCHIP

PERIPHERAL

4OONCHIP

PERIPHERAL

/UTPUT

CONTROL

!NALOG

ONOFF

0ULL

0ULL

ONOFF

)/PIN

6

$$

6

$$

6

33

6

33

44,3CHMITT

TRIGGER

6

33

6

$$?&4

0ROTECTION

DIODE

0ROTECTION

DIODE

ONOFF

)NPUTDRIVER

/UTPUTDRIVER

DOWN

UP

0-/3

.-/3

2EAD

"ITSETRESETREGISTERS

7RITE

!NALOG

)NPUTDATAREGISTER

AIB

Loading...

Loading...