RM0390 Rev 4 927/1328

RM0390 SPDIF receiver interface (SPDIFRX)

929

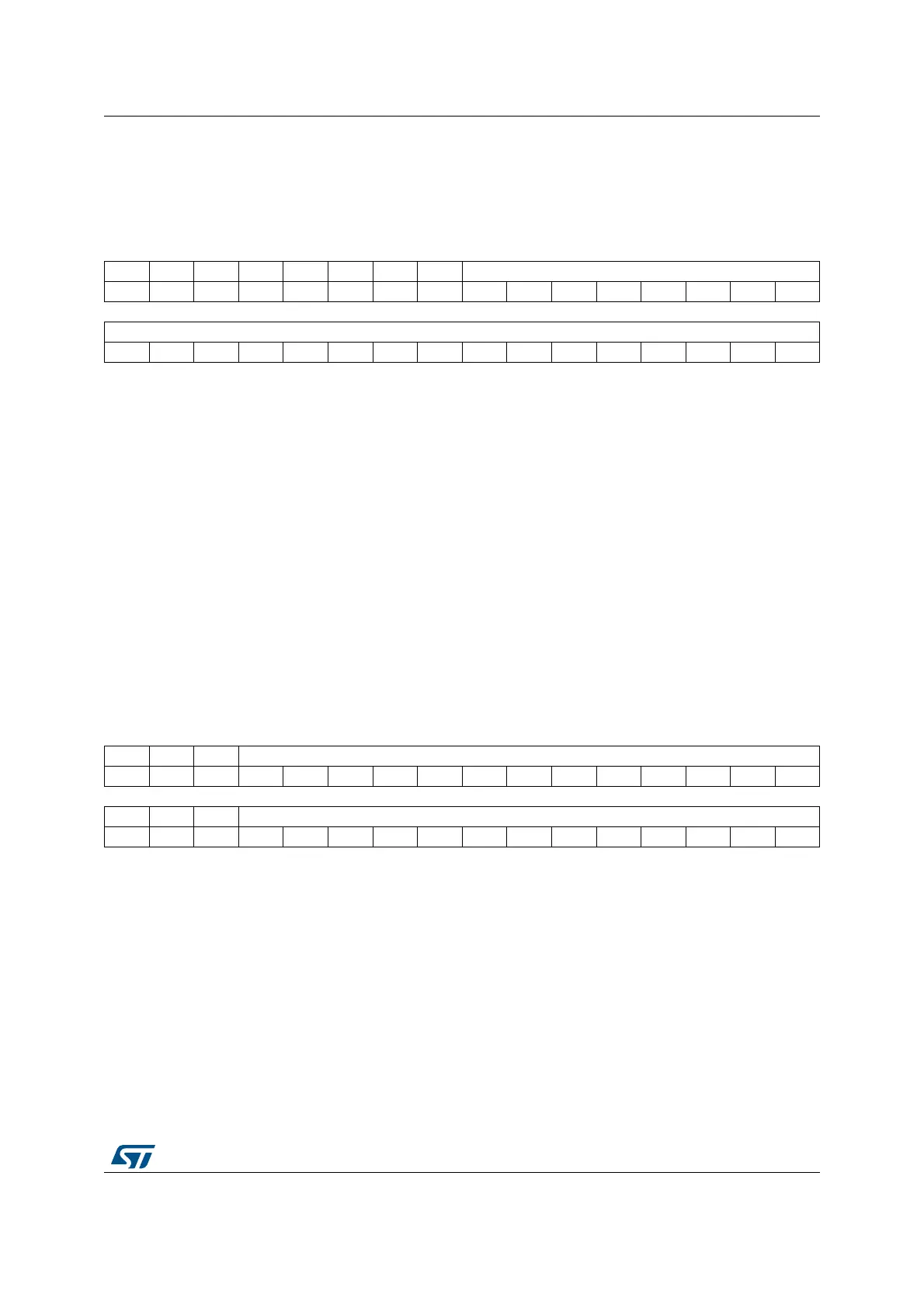

27.5.8 Channel status register (SPDIFRX_CSR)

Address offset: 0x14

Reset value: 0x0000 0000

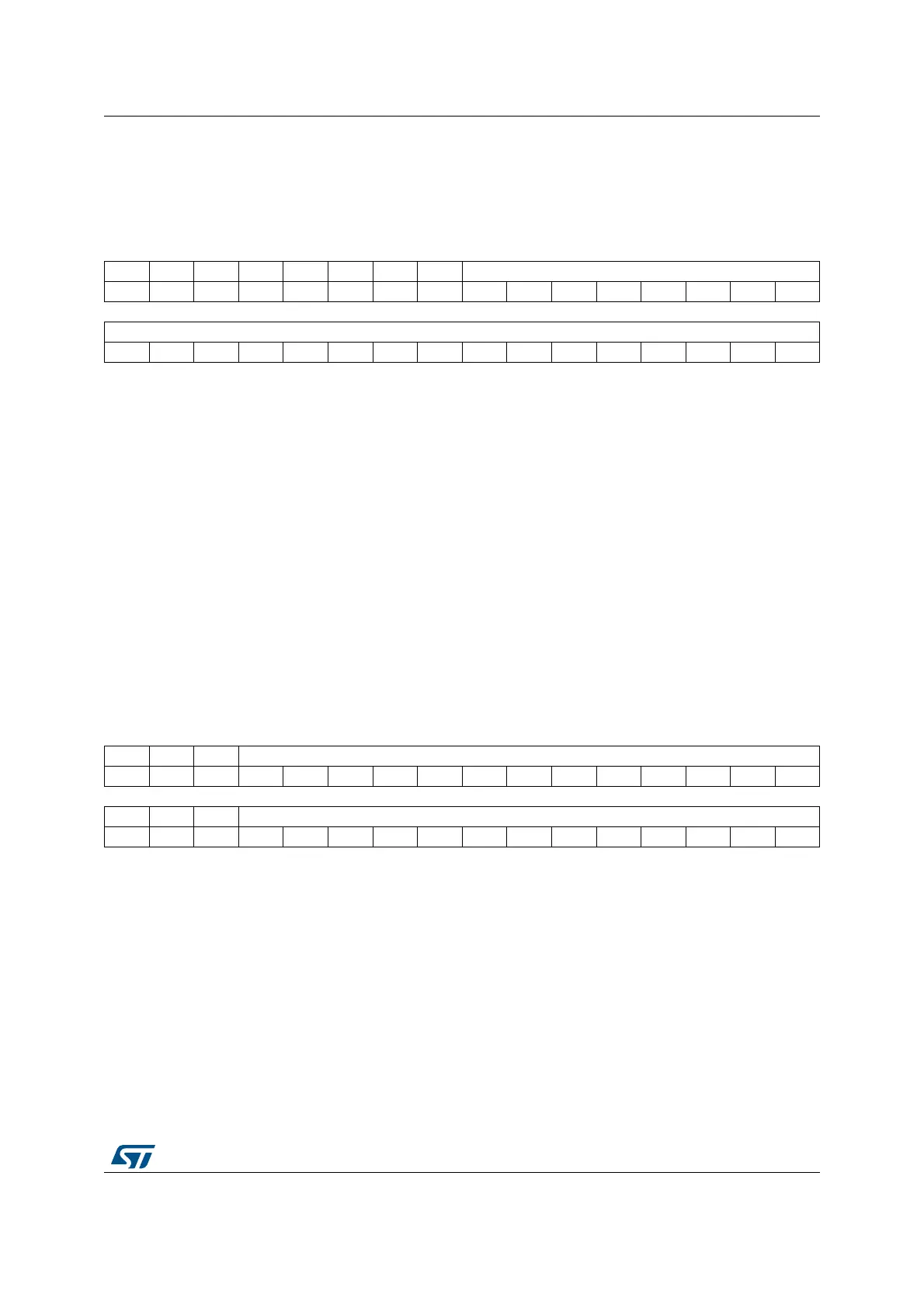

27.5.9 Debug information register (SPDIFRX_DIR)

Address offset: 0x18

Reset value: 0x0000 0000

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. SOB CS[7:0]

rrrrrrrrr

1514131211109876543210

USR[15:0]

rrrrrrrrrrrrrrrr

Bits 31:25 Reserved, must be kept at reset value.

Bit 24 SOB: Start Of Block

This bit indicates if the bit CS[0] corresponds to the first bit of a new block

0: CS[0] is not the first bit of a new block

1: CS[0] is the first bit of a new block

Bits 23:16 CS[7:0]: Channel A status information

Bit CS[0] is the oldest value

Bits 15:0 USR[15:0]: User data information

Bit USR[0] is the oldest value, and comes from channel A, USR[1] comes channel B.

So USR[n] bits come from channel A is n is even, otherwise they come from channel B.

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. TLO[12:0]

rrrrrrrrrrrrr

1514131211109876543210

Res. Res. Res. THI[12:0]

rrrrrrrrrrrrr

Bits 31:29 Reserved, must be kept at reset value.

Loading...

Loading...