USB on-the-go full-speed/high-speed (OTG_FS/OTG_HS) RM0390

1144/1328 RM0390 Rev 4

31.15.17 Host-mode registers

Bit values in the register descriptions are expressed in binary unless otherwise specified.

Host-mode registers affect the operation of the core in the host mode. Host mode registers

must not be accessed in device mode, as the results are undefined. Host mode registers

can be categorized as follows:

31.15.18 OTG host configuration register (OTG_HCFG)

Address offset: 0x400

Reset value: 0x0000 0000

This register configures the core after power-on. Do not make changes to this register after

initializing the host.

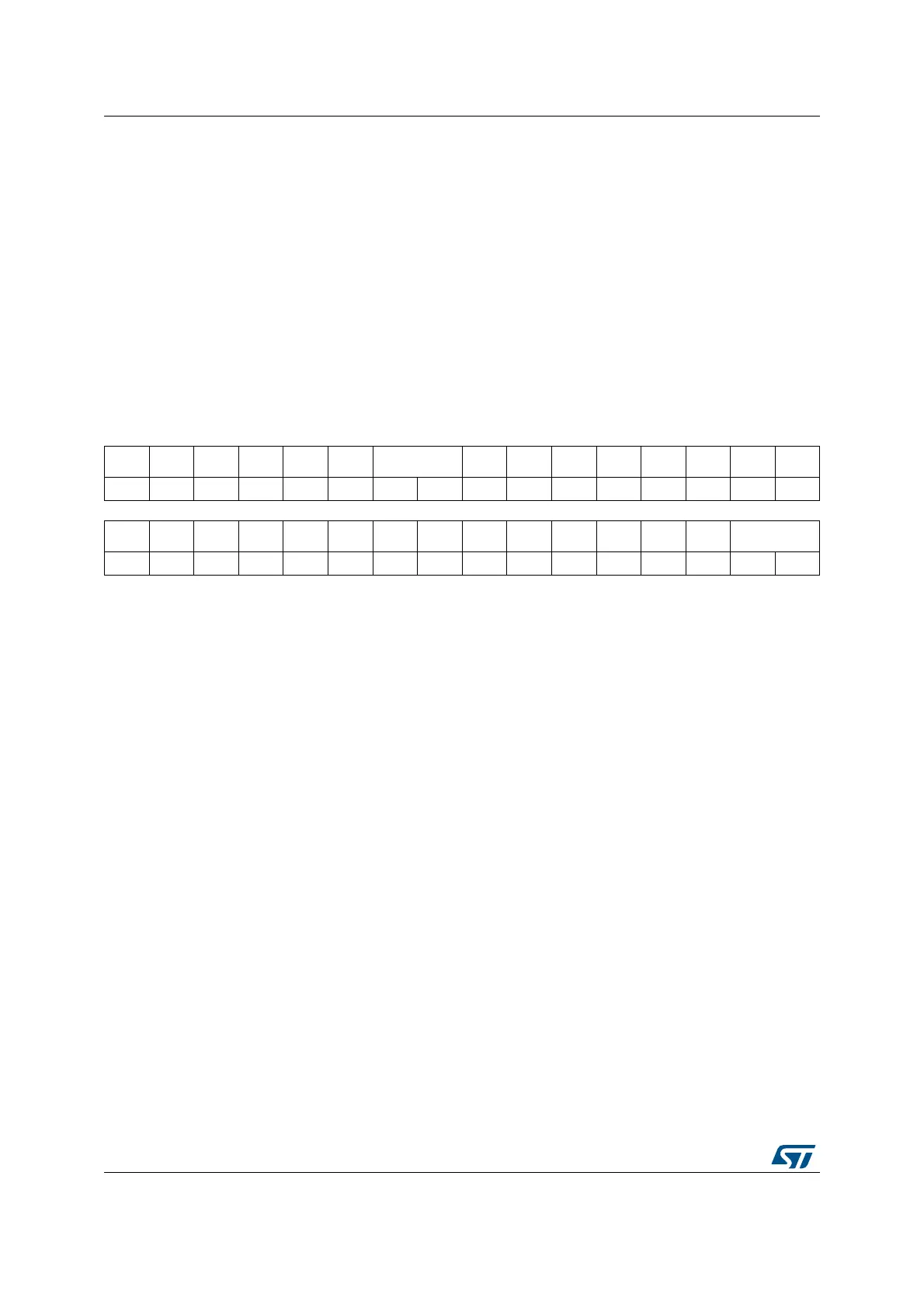

31 30 29 28 27 26 25 24 23 22 21 20 19 18 17 16

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res.

1514131211109876543210

Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. Res. FSLSS FSLSPCS[1:0]

rrwrw

Bits 31:3 Reserved, must be kept at reset value.

Bit 2 FSLSS: FS- and LS-only support

The application uses this bit to control the core’s enumeration speed. Using this bit, the

application can make the core enumerate as an FS host, even if the connected device

supports HS traffic. Do not make changes to this field after initial programming.

1: FS/LS-only, even if the connected device can support HS (read-only).

Bits 1:0 FSLSPCS[1:0]: FS/LS PHY clock select

When the core is in FS host mode

01: PHY clock is running at 48 MHz

Others: Reserved

When the core is in LS host mode

00: Reserved

01: Select 48 MHz PHY clock frequency

10: Select 6 MHz PHY clock frequency

11: Reserved

Note: The FSLSPCS must be set on a connection event according to the speed of the

connected device (after changing this bit, a software reset must be performed).

Loading...

Loading...