Universal synchronous asynchronous receiver transmitter (USART) RM0390

824/1328 RM0390 Rev 4

has been written). This means that it is not possible to receive a synchronous data without

transmitting data.

The LBCL, CPOL and CPHA bits have to be selected when both the transmitter and the

receiver are disabled (TE=RE=0) to ensure that the clock pulses function correctly. These

bits should not be changed while the transmitter or the receiver is enabled.

It is advised that TE and RE are set in the same instruction in order to minimize the setup

and the hold time of the receiver.

The USART supports master mode only: it cannot receive or send data related to an input

clock (SCLK is always an output).

Figure 290. USART example of synchronous transmission

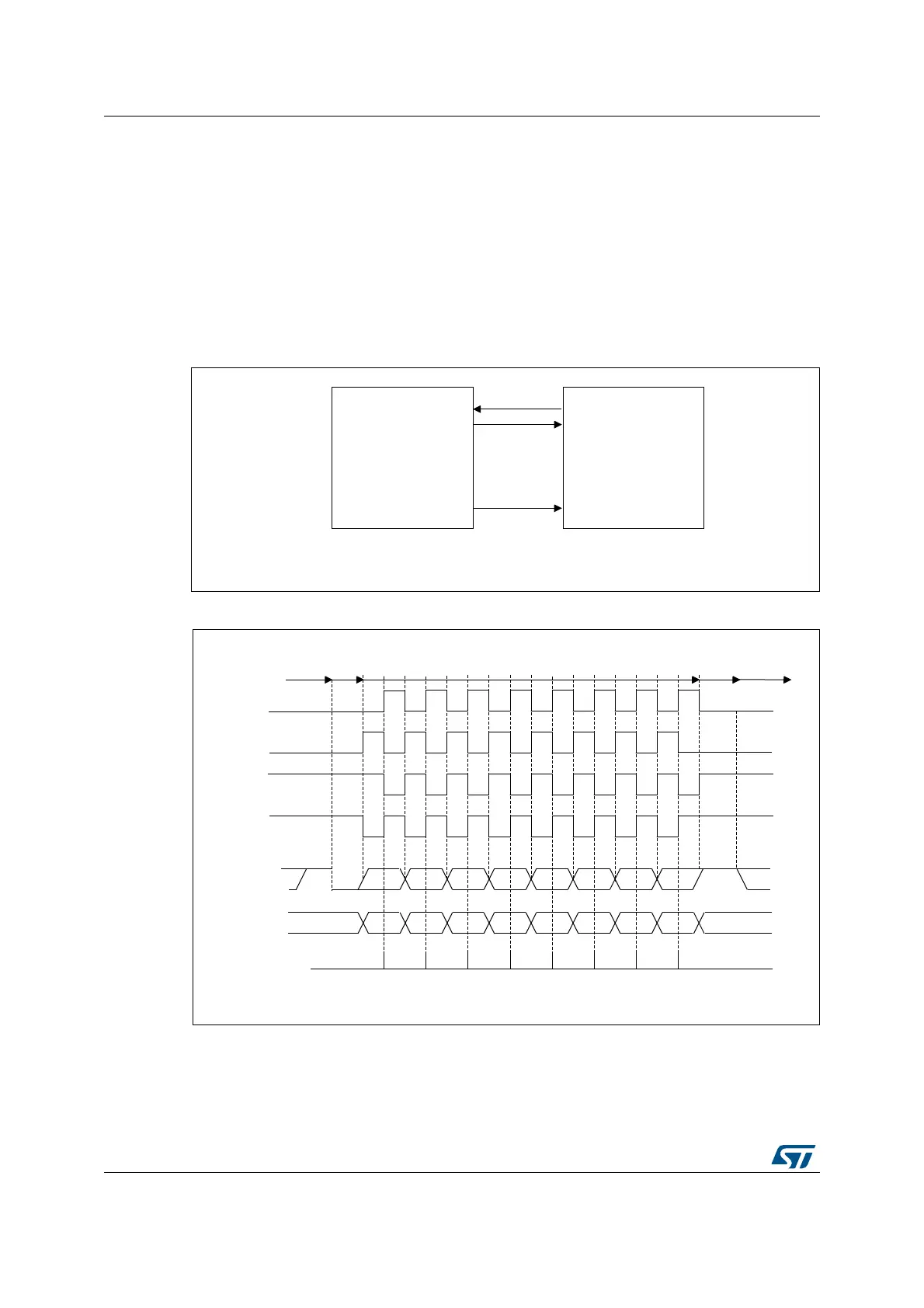

Figure 291. USART data clock timing diagram (M=0)

06Y9

86$57

6\QFKURQRXVGHYLFH

HJVODYH63,

5;

7;

'DWDRXW

'DWDLQ

&ORFN

6&/.

06Y9

06%

06%

/6%

/6%

6WDUW

6WDUW 6WRS

,GOHRUSUHFHGLQJ

WUDQVPLVVLRQ

,GOHRUQH[W

WUDQVPLVVLRQ

/%&/ELWFRQWUROVODVWGDWDSXOVH

&DSWXUHVWUREH

'DWDRQ5;

IURPVODYH

'DWDRQ7;

IURPPDVWHU

&ORFN&32/ &3+$

&ORFN&32/ &3+$

&ORFN&32/ &3+$

&ORFN&32/ &3+$

6WRS

0ELWV GDWDELWV

Loading...

Loading...