RM0390 Rev 4 913/1328

RM0390 SPDIF receiver interface (SPDIFRX)

929

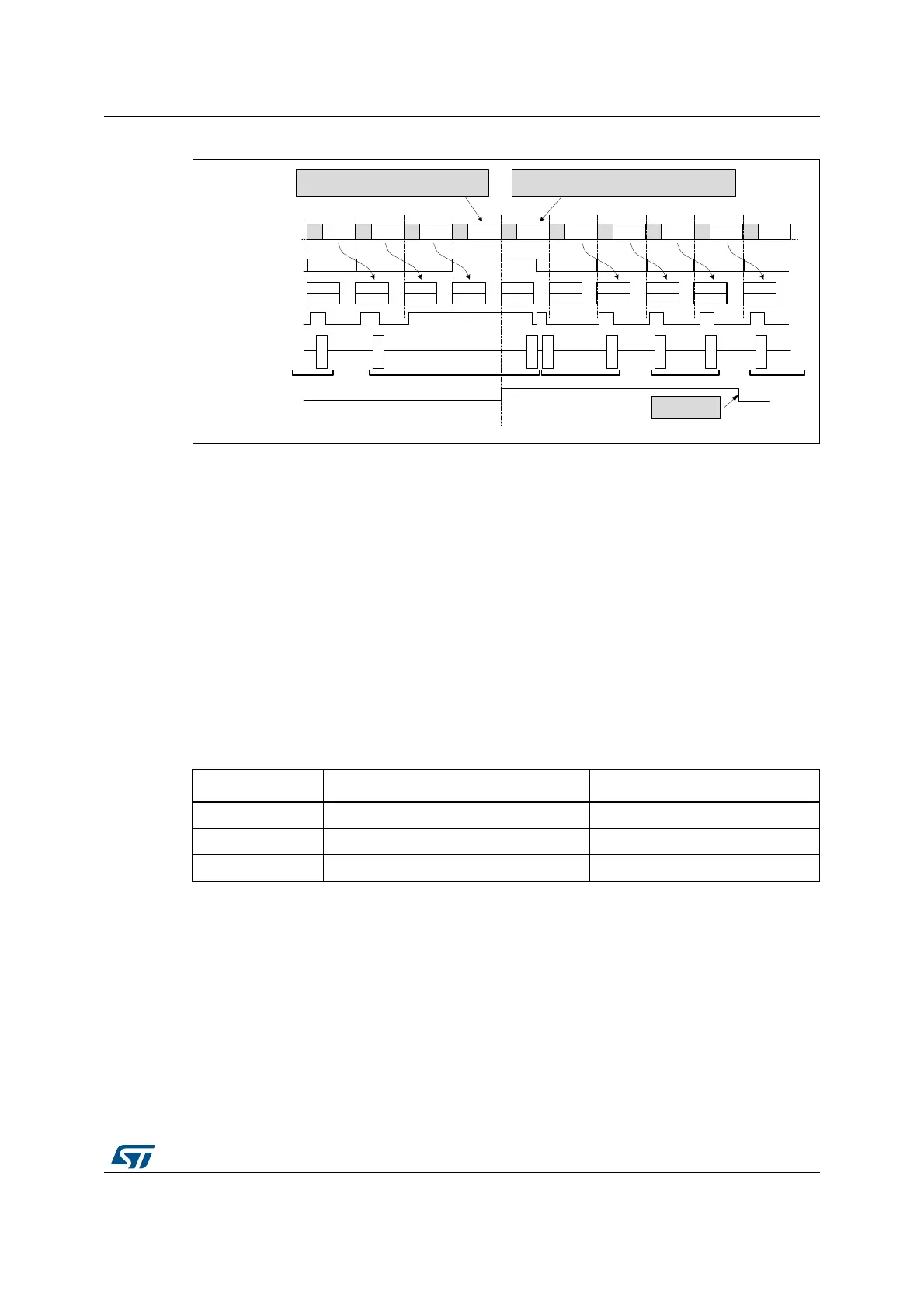

Figure 352. S/PDIF overrun error when RXSTEO = 1

27.3.9 Clocking strategy

The SPDIFRX block needs two different clocks:

• The APB1 clock (PCLK1), which is used for the register interface,

• The SPDIFRX_CLK which is mainly used by the SPDIFRX_DC part. Those clocks are

not supposed to be phase locked, so all signals crossing those clock domains are re-

synchronized (SYNC block on Figure 338).

In order to decode properly the incoming S/PDIF stream the SPDIFRX_DC shall re-sample

the received data with a clock at least 11 times higher than the maximum symbol rate, or

704 times higher than the audio sample rate. For example if the user expects to receive a

symbol rate to up to 12.288 MHz, the sample rate shall be at least 135.2 MHz. The clock

used by the SPDIFRX_DC is the SPDIFRX_CLK.

The frequency of the PCLK1 must be at least equal to the symbol rate.

27.3.10 DMA Interface

The SPDIFRX interface is able to perform communication using the DMA.

Note: The user should refer to product specifications for availability of the DMA controller.

The SPDIFRX offers two independent DMA channels:

• A DMA channel dedicated to the data transfer

• A DMA channel dedicated to the channel status and user data transfer

The DMA mode for the data can be enabled for reception by setting the RXDMAEN bit in the

SPDIFRX_CR register. In this case, as soon as the SPDIFRX_DR is not empty, the

0 &K$ : &K% % &K$ : &K% 0 &K$ : &K% 0 &K$ : &K% % &K$ : &K%

5;B%8))8//

&K%

63',)5;B'0$B5(4

5;B%8)DQG

63',)5;B'5FRQWHQW

&K$

&K%

&K%

&K$

&K%

&K$

&K%

&K$

&K%

&K$

63',)5;B,1

63',)5;B,54

$FNQRZOHGJHG

E\6:

&K%FDQQRWEHZULWWHQLQWRWKH5;B%8)

EHFDXVHLWLV)8//Î2YHUUXQ

&K$FDQQRWEHZULWWHQLQWRWKH5;B%8)HYHQLIWKH

5;B%8)LVQRW)8//LQRUGHUWRDYRLGPLVDOLJQPHQWV

&K%

&K$

&K%

&K$

&K%

&K$

&K%

&K$

6DPSOHVVWRUHGLQWR

PHPRU\

06Y9

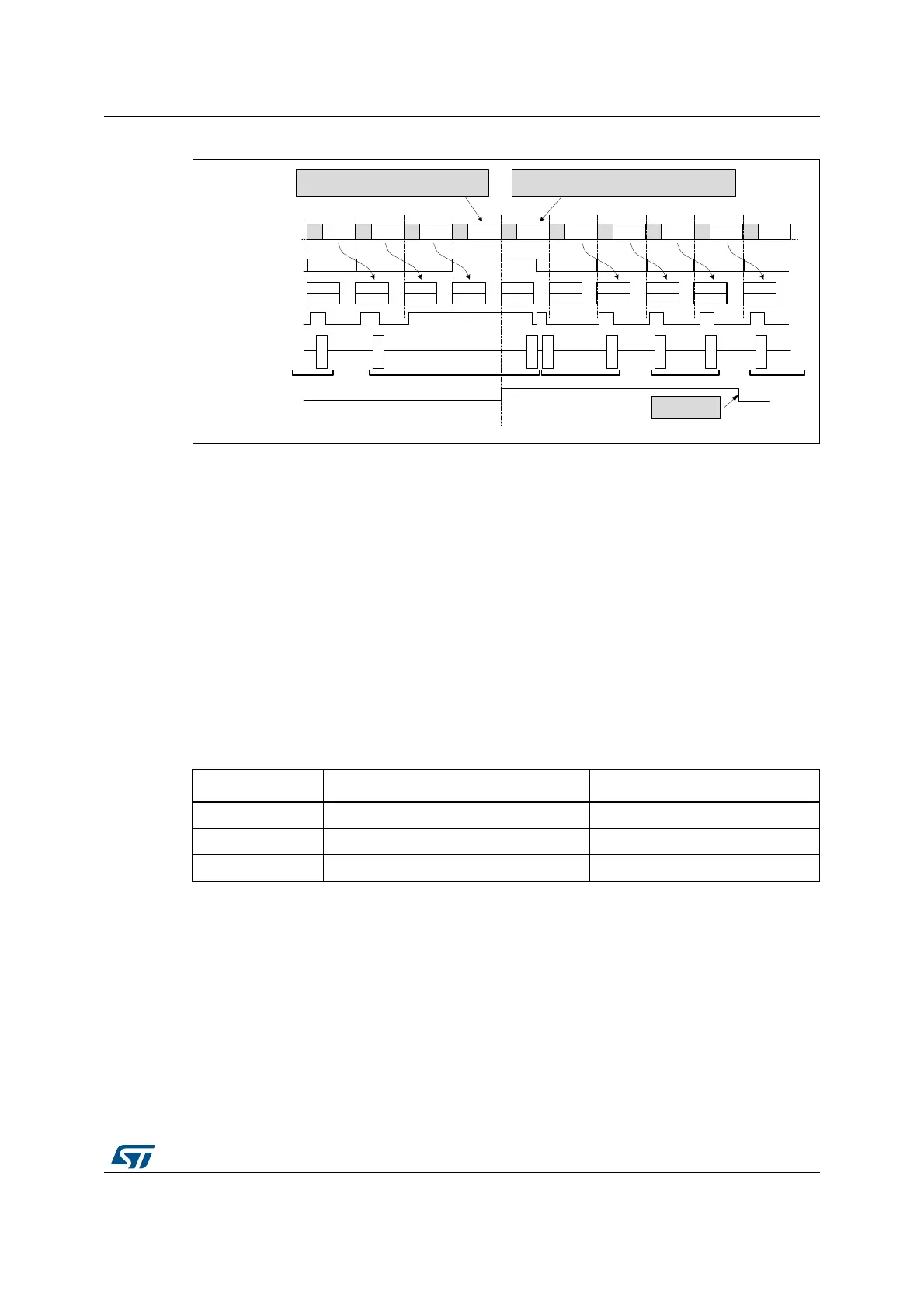

Table 168. Minimum SPDIFRX_CLK frequency versus audio sampling rate

Symbol Rate Minimum SPDIFRX_CLK frequency Comments

3.072 MHz 33.8 MHz For 48 kHz stream

6.144 MHz 67.6 MHz For 96 kHz stream

12.288 MHz 135.2 MHz For 192 kHz stream

Loading...

Loading...